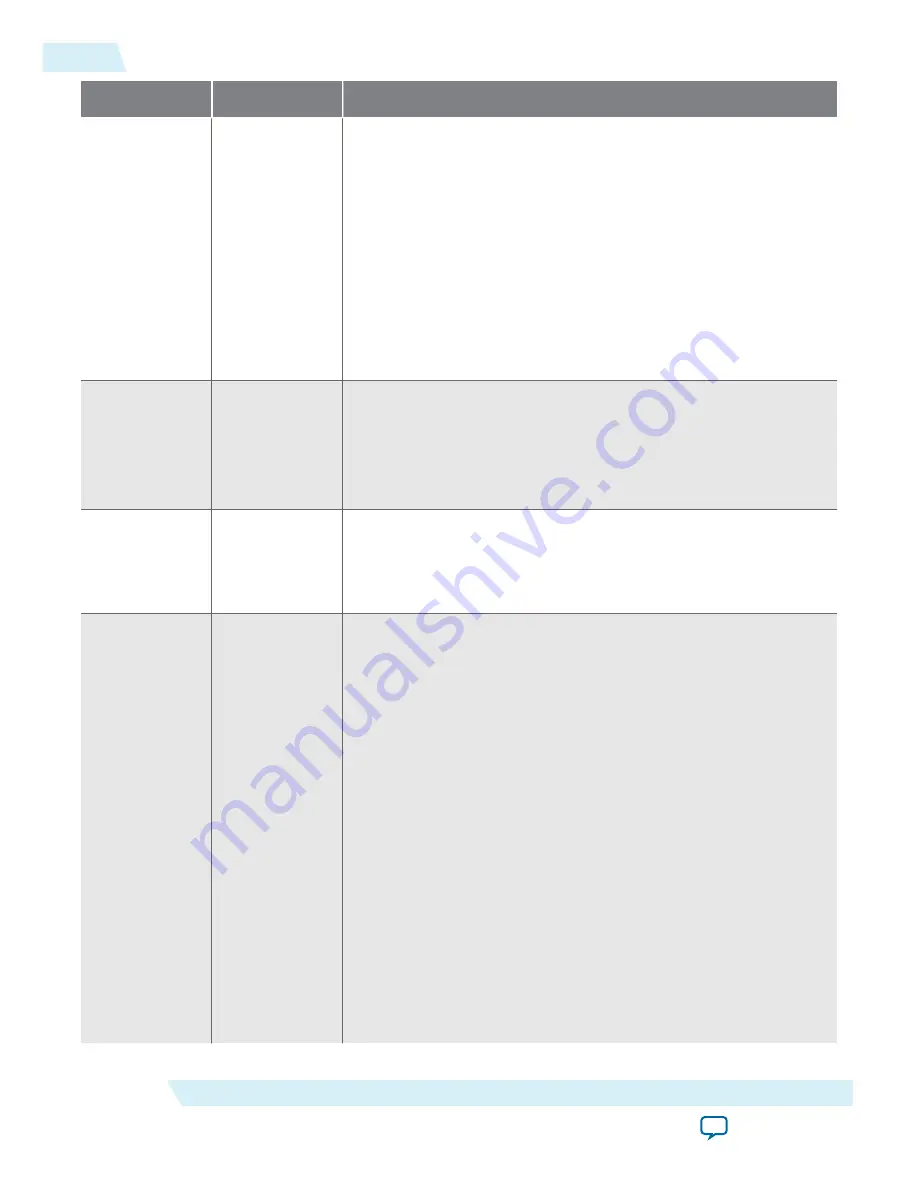

Date

Version

Changes Made

• Added an immediate write mode for single dword writes. The data

is stored in the

WR_RC_LOW_SRC_ADDR

register. The new

Immediate Write Mode

bit of the DMA Descriptor controls this

functionality.

• Corrected

TLP Support Comparison for all Hard IP for PCI Express

IP Cores

entries. Only Completions with and without data are

supported for the Avalon-MM DMA interface. Message Reqeusts

with and without data are not supported for the Avalon-M

interface.

• Added optional Hard IP Status bus signals to the

Avalon-MM

DMA Bridge with Internal Descriptor Controller

and

Avalon-MM

DMA Bridge with External Descriptor Controller

figures.

2015.06.05

15.0

Added note in

Physical Layout of Hard IP In Arria 10 Devices

to

explain Arria 10 design constraint that requires that if the lower HIP

on one side of the device is configured with a Gen3 x4 or Gen3 x8 IP

core, and the upper HIP on the same side of the device is also

configured with a Gen3 IP core, then the upper HIP must be

configured with a x4 or x8 IP core.

2015.05.14

15.0

Made the following changes to the user guide:

• Added Enable Hard IP Status Bus when using the AVMM

interface parameter in

Interface System Settings

. This parameter

is available in the IP core v15.0 and later.

2015.05.04

15.0

• Added Enable Altera Debug Master Endpoint (ADME)

parameter to support optional Native PHY register programming

with the Altera System Console.

• Added support for downstream burst read request for a payload of

size up to 4 KB, if Enable burst capability for RXM BAR2 port is

turned on in the Parameter Editor. Previous maximum

downstream read request payload size was 512 bytes. Refer to

Arria 10 Avalon-MM DMA for PCI Express

on page 10-8.

• Corrected the allowed value of the Maximum payload size

parameter for Avalon-MM DMA IP core variations, in

Device

Capabilities

on page 4-8.

• Corrected the supported variations to include Gen3 x2.

• Removed the High and Maximum values for the RX Buffer credit

allocation -performance for received requests parameter. These

values are no longer valid settings. Refer to

System Settings

.

• Enhanced descriptions of channel placement, added fPLL

placement for Gen1 and Gen2 data rates, and added master CGB

location, in

Physical Layout of Hard IP In Arria 10 Devices

on

page 5-1.

• Reinstated

Design Implementation

on page 11-1 chapter.

B-2

Revision History for the Avalon-MM Interface with DMA

UG-01145_avmm_dma

2015.11.02

Altera Corporation

Additional Information

Send Feedback