3.1

Overview of high-speed design

When designing a target board that will be connected to a DSTREAM-PT system, it is important to use

good digital design practice to achieve high Signal Integrity (SI).

While many target boards already take SI into consideration for trace signals, it is also important to use

the same design methodology for the debug signals. To achieve the high-data throughput that is required

to debug modern target systems, DSTREAM-ST units are designed to drive their JTAG interfaces at up

to 180MHz. To drive at this frequency, DSTREAM-ST units use fast output drivers with short rise-times.

Note

A target system might work perfectly when it is connected to an older or slower debug unit, but it could

fail to work with DSTREAM-ST because of the faster rise-times.

There are many design rules that you can implement to ensure high SI in the debug and trace interfaces:

Note

While these rules apply to all digital signals, Arm recommends giving special attention to the clock

signals,

TCK

,

RTCK

, and

TRACECLK

.

•

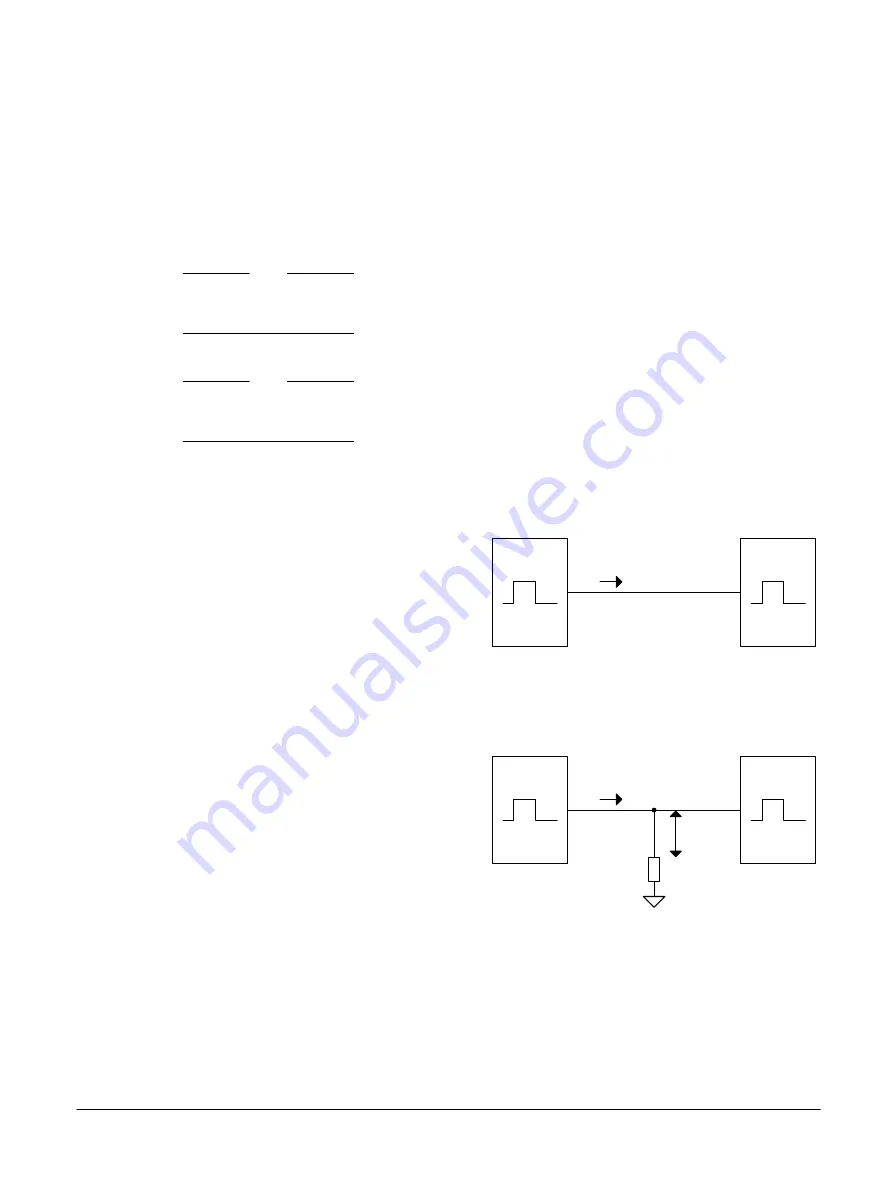

Avoid stubs

Where possible, debug and trace signals should be point-to-point between the driver and receiver of

the signal with no T-junctions or branches leading to other circuitry on the target board.

Target

Device

Debug

Connector

Figure 3-1 Point-to-point signal

For debug signals, pull-up or pull-down resistors are often required. Pull-up or pull-down resistors

might create a branch or

stub

in the signal path. It is important to keep the stub length in the signal

path as short as possible.

Target

Device

Debug

Connector

Stub

length

Figure 3-2 Stub length

If a signal is routed with a long stub, the signal from the driver is split two ways when it reaches the

T-junction. The signal that reaches the target device initially has a lower amplitude until the other half

of the signal has reflected back from the end of the stub. The reflection has the effect of creating a

stepped signal at the target device. A stepped signal at the target device can cause extra false signal

edges to be received.

3 Target board design

3.1 Overview of high-speed design

101714_0100_02_en

Copyright © 2019 Arm Limited or its affiliates. All rights reserved.

3-52

Non-Confidential