E0C6006 TECHNICAL MANUAL

EPSON

11

CHAPTER 4: PERIPHERAL CIRCUITS AND OPERATION (Watchdog Timer)

4.2 Watchdog Timer

4.2.1 Configuration of watchdog timer

The E0C6006 has a built-in watchdog timer that operates with a divided clock from the OSC1 as the

source clock. The watchdog timer must be reset cyclically by the software while it operates. If the watch-

dog timer is not reset in at least 3–4 seconds (when f

OSC1

is 32.768 kHz), it resets the CPU.

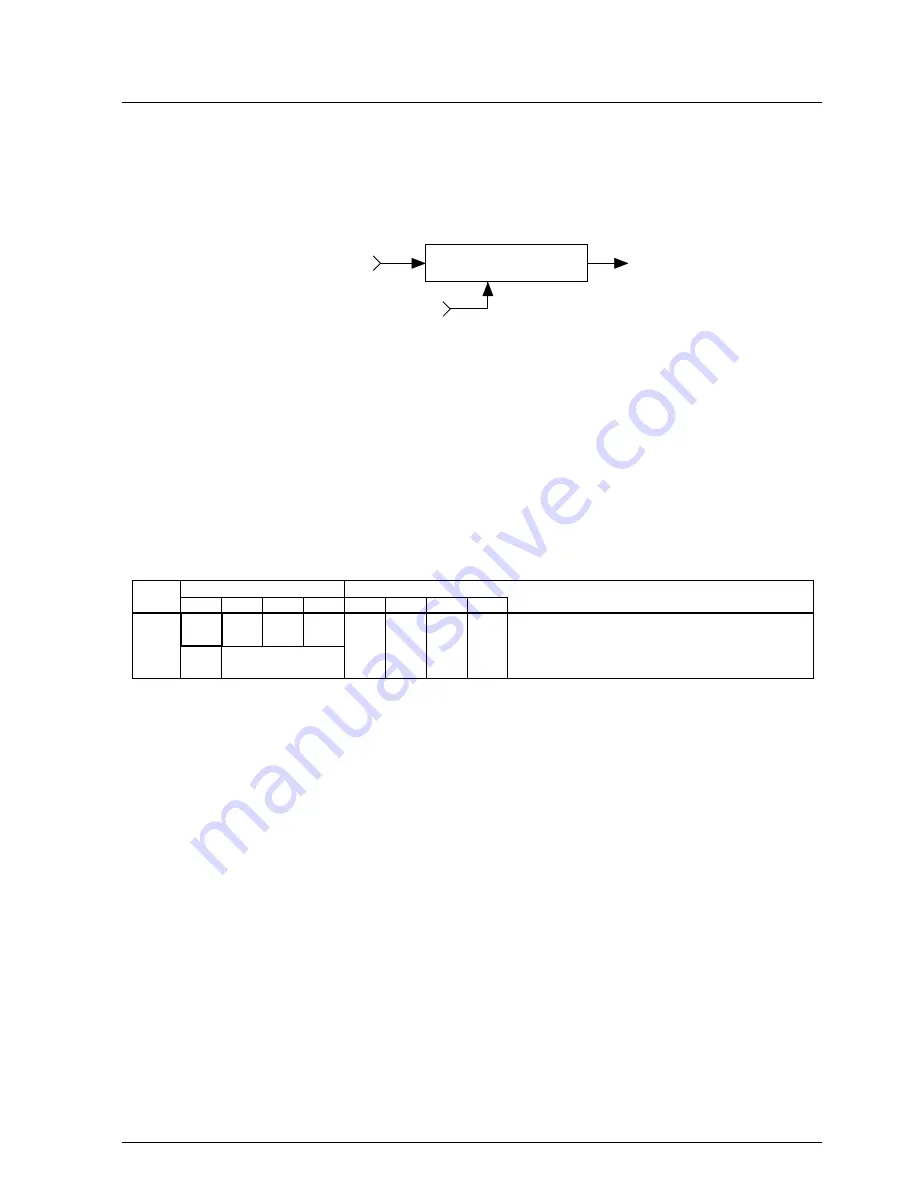

Figure 4.2.1.1 is the block diagram of the watchdog timer.

Watchdog timer

Initial reset

signal

OSC1 dividing clock

Watchdog timer reset signal

Fig. 4.2.1.1 Watchdog timer block diagram

Watchdog timer reset processing in the program's main routine enables detection of program overrun,

such as when the main routine's watchdog timer processing is bypassed. Ordinarily this routine is

incorporated where periodic processing takes place, just as for the timer interrupt routine.

The watchdog timer operates in the HALT mode. If a HALT status continues for 3–4 seconds, the watch-

dog timer generates a CPU reset signal.

The watchdog timer function can be nullified by using the mask option.

4.2.2 I/O memory of watchdog timer

Table 4.2.2.1 shows the I/O address and control bit for the watchdog timer.

Table 4.2.2.1 Control bit of watchdog timer

Address

Comment

D3

D2

Register

D1

D0

Name

Init

∗

1

1

0

0F1H

WDRST

IT2

IT8

IT32

W

R

WDRST

IT2

∗

4

IT8

∗

4

IT32

∗

4

Reset

0

0

0

Reset

Yes

Yes

Yes

–

No

No

No

Watchdog timer reset

Interrupt factor flag (clock timer 2 Hz)

Interrupt factor flag (clock timer 8 Hz)

Interrupt factor flag (clock timer 32 Hz)

∗

1

∗

2

Initial value at initial reset

Not set in the circuit

∗

5 Undefined

∗

3

∗

4

Always "0" being read

Reset (0) immediately after being read

WDRST: Watchdog timer reset (0F1H•D3)

Resets the watchdog timer.

When "1" is written: Watchdog timer is reset

When "0" is written: No operation

Reading: Always "0"

When "1" is written to WDRST, the watchdog timer is reset and restarts immediately after that. When "0"

is written, no operation results.

This bit is dedicated for writing, and is always "0" for reading.

4.2.3 Programming note

When the watchdog timer is being used, the software must reset it within 3-second cycles.