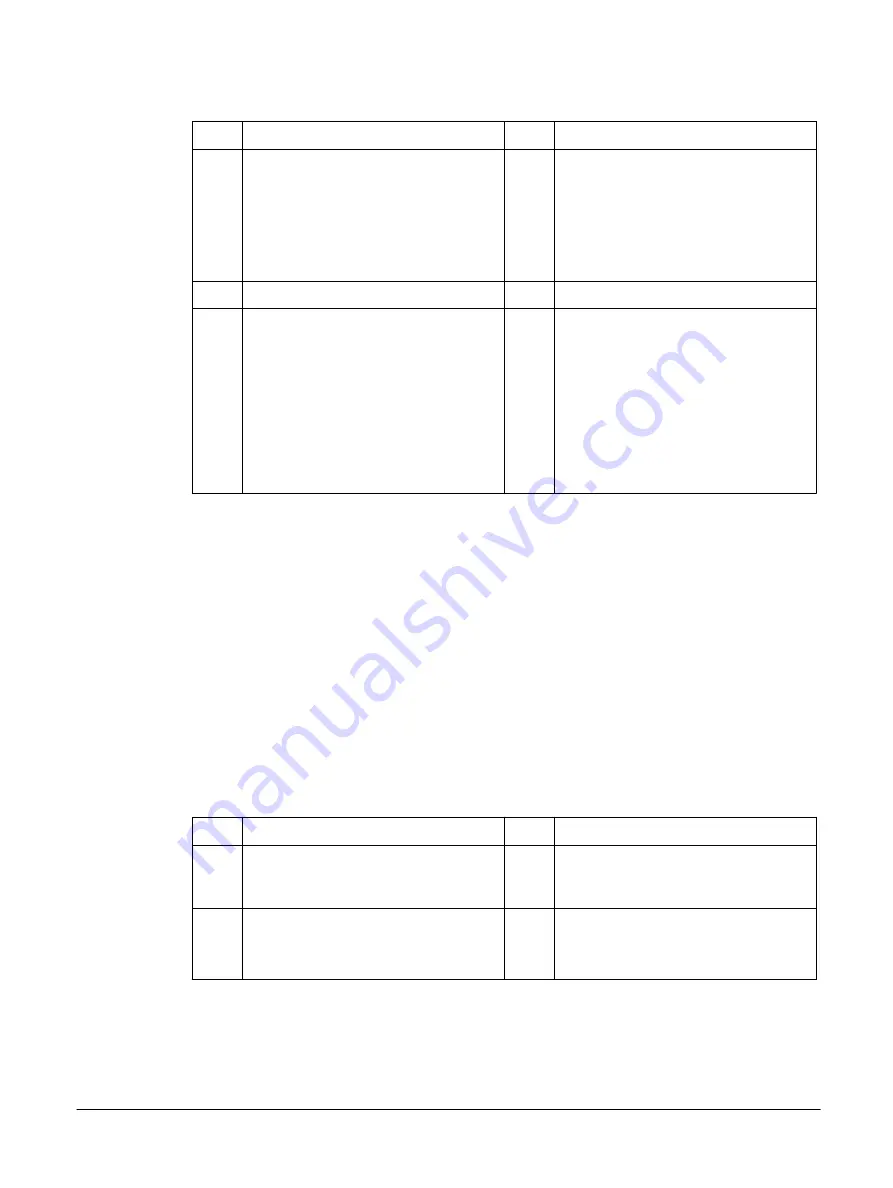

Table 4-114 IOFPGA_TSIF_PAD_CTRL Register bit assignments (continued)

Bits

Name

Type

Function

[4]

IO_SR_IOFPGA_AXI_TSIF_DATA

RW

Slew rate control of IOFPGA AXI TSIF

output pads IOFPGA_TSIF_DATA_O[7:0]:

0b0

: Fast.

0b1

: Slow.

Reset value

0b1

.

[3:2]

-

-

Reserved.

[1:0]

IO_DS_IOFPGA_AXI_TSIF_DATA

RW

Drive strength control of IOFPGA AXI TSIF

output pads IOFPGA_TSIF_DATA_O[7:0]:

0b00

: 2mA.

0b01

: 8mA.

0b10

: 4mA.

0b11

: 12mA.

Reset value

0b01

.

4.5.84

APB_CTRL_CLR Register

The APB_CTRL_CLR Register characteristics are:

Purpose

Controls reversion to serial control of the register at the specified base address.

Usage constraints

There are no usage constraints.

Configurations

Available in all N1 board configurations.

Memory offset and full register reset value

See

4.5.1 Serial Configuration Control registers summary

The following table shows the APB_CTRL_CLR Register bit assignments.

Table 4-115 APB_CTRL_CLR Register bit assignments

Bits

Name

Type

Function

[31:12] NUMBER

RW

Writing

0xA50F5

to this field sets the register,

whose base address bits[11:0] specify, to serial

control.

[11:0]

BASE_ADDRESS

RW

Base address of register which reverts to serial

control when

0xA50F5

is written to

bits[31:12].

4.5.85

PID4 Register

The PID4 Register characteristics are:

Purpose

Stores peripheral identification information.

4 Programmers model

4.5 Serial Configuration Control registers

101489_0000_02_en

Copyright © 2019, 2020 Arm Limited or its affiliates. All rights

reserved.

4-191

Non-Confidential - Beta