4.4

System Security Control registers

The

System Security Control

(SSC) interface in the N1 SoC controls system-wide security features.

These features include the following:

• Selection of and internal sources for Debug Authentication signals

• General Purpose register for secure state storage

The registers are in the Always-on power domain so their states are maintained when the system is

powered down except when VSYS is powered down.

This section contains the following subsections:

•

4.4.1 System Security Control registers summary

•

4.4.2 SSC_DBGCFG_STAT Register

•

4.4.3 SSC_DBGCFG _SET Register

•

4.4.4 SSC_DBGCFG _CLR Register

•

•

•

•

4.4.8 SSC_SW_SCRATCH Registers

•

•

4.4.10 SSC_SW_CAPCTRL Register

•

•

•

•

•

•

•

•

•

4.4.1

System Security Control registers summary

The base memory address of the SSC registers is

0x0_2A42_0000

in the subystem peripherals region of

the

Application Processor

(AP) memory map.

The following table shows the SSC registers in offset order from the base memory address. Undefined

registers are reserved. Software must not attempt to access these registers.

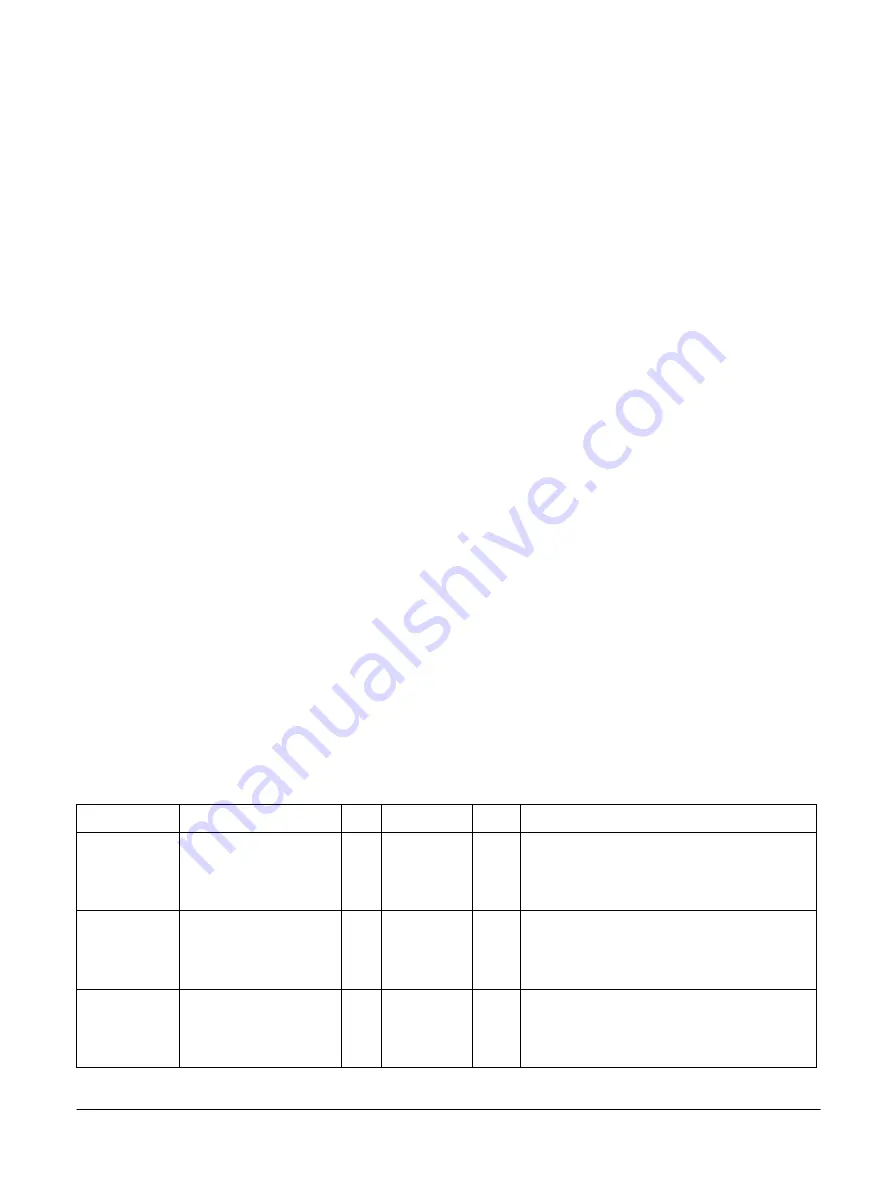

Table 4-13 SCC registers summary

Offset

Name

Type Reset

Width Description

0x0010

SSC_DBGCFG_STAT

RO

0x0001_0000

32

Debug authentication configuration status

See

4.4.2 SSC_DBGCFG_STAT Register

.

0x0014

SSC_DBGCFG _SET

WO

N/A

32

Debug authentication configuration set.

See

4.4.3 SSC_DBGCFG _SET Register

.

0x0018

SSC_DBGCFG _CLR

WO

N/A

32

Debug authentication configuration clear.

See

4.4.4 SSC_DBGCFG _CLR Register

.

4 Programmers model

4.4 System Security Control registers

101489_0000_02_en

Copyright © 2019, 2020 Arm Limited or its affiliates. All rights

reserved.

4-105

Non-Confidential - Beta