DIVXU

DIVXU (DIVide eXtend as Unsigned)

Divide

DIVXU Instruction, Zero Divide, and Overflow

Zero divide and overflow are not detected in the DIVXU instruction. A program like the following

can detect zero divisors and avoid overflow.

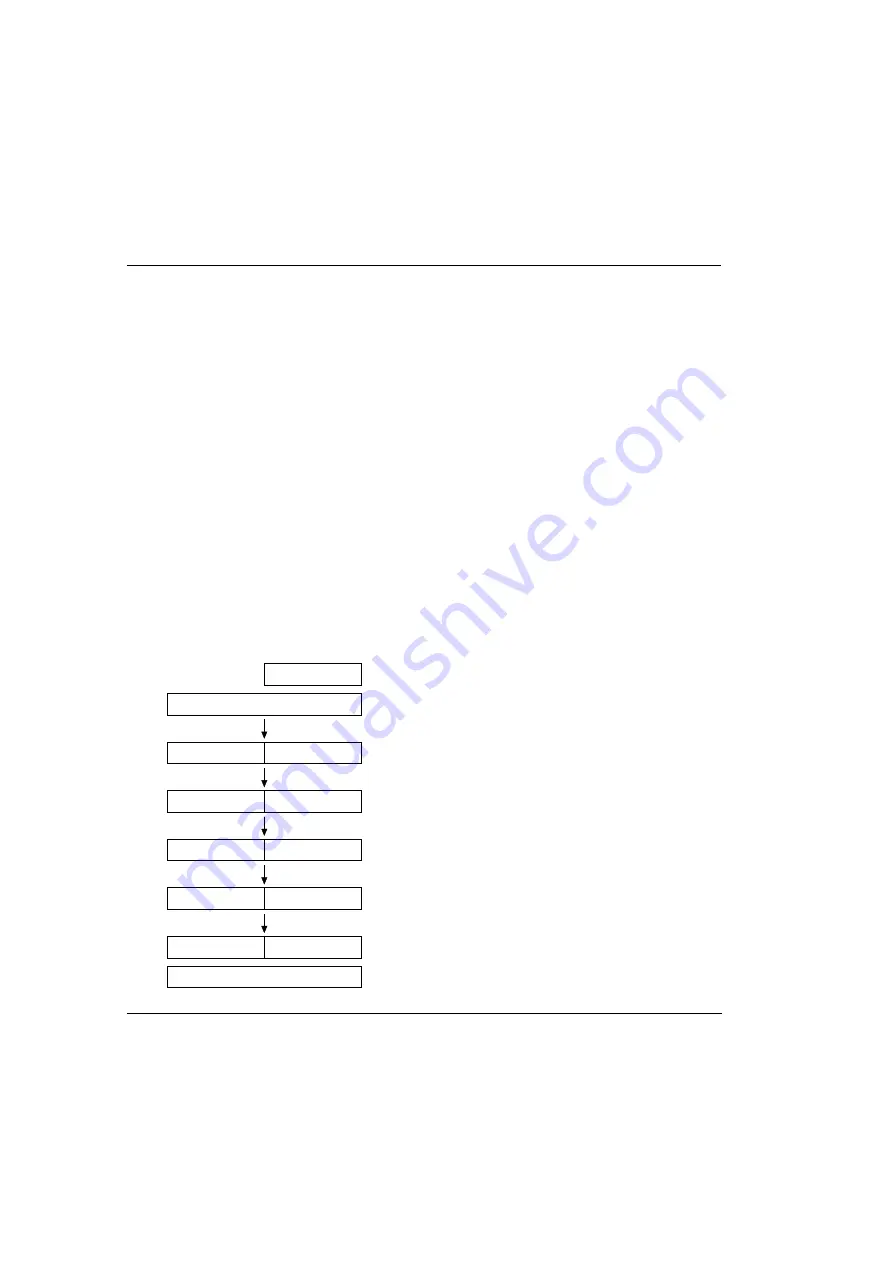

1. Programming solutions for DIVXU.B R0L, R1

Example 1: Divide upper 8 bits and lower 8 bits of 16-bit dividend separately and obtain 16-bit

quotient

CMP.B

#0, R0L

; R0L = 0? (Zero divisor?)

BEQ

ZERODIV

; Branch to ZERODIV if R0L = 0

MOV.B

R1H,R2L

;

Copy upper 8 bits of dividend to R2L and

EXTU.W

R2

(*1)

.

;

zero-extend to 16 bits

DIVXU.B

R0L, R2

(*2)

; Divide upper 8 bits of dividend

MOV.B

R2H, R1H

(*3)

; R2H

→

R1H (store partial remainder in R1H)

DIVXU.B

R0L, R1

(*4)

; Divide lower 8 bits of dividend (including repeated division of

upper 8 bits)

MOV.B

R2L, R2H

;

Store upper part of quotient in R2H

MOV.B

R1L, R2L

(*5)

;

Store lower part of quotient in R2L

RTS

ZERODIV:

; Zero-divide handling routine

The resulting operation is 16 bits ÷ 8 bits

→

quotient (16 bits) and remainder (8 bits), and no

overflow occurs. The 16-bit quotient is stored in R2, the 8-bit remainder in R1H.

Remainder

Quotient (low)

Remainder

Quotient (low)

Quotient

R1

R2

R2

R1

R1

R1

R2

R0L

( 1)

*

( 2)

*

( 3)

*

( 4)

*

( 5)

*

Divisor

Dividend

Sign extension

Dividend (high)

Remainder (part) Quotient (high)

Remainder (part)

Dividend (low)

92