2.2.9 BIAND

BIAND (Bit Invert AND)

Bit Logical AND

Operation

C

∧

[¬ (<bit No.> of <EAd>)]

→

C

Assembly-Language Format

BIAND

#xx:3, <EAd>

Operand Size

Byte

Condition Code

H: Previous value remains unchanged.

N: Previous value remains unchanged.

Z: Previous value remains unchanged.

V: Previous value remains unchanged.

C: Stores the result of the operation.

I

UI

H

U

N

Z

V

C

—

—

—

—

—

—

—

↕

Description

This instruction ANDs the inverse of a specified bit in the destination operand with the carry bit

and stores the result in the carry bit. The bit number is specified by 3-bit immediate data. The

destination operand contents remain unchanged.

Available Registers

Rd:

R0L to R7L, R0H to R7H

ERd: ER0 to ER7

Operand Format and Number of States Required for Execution

Note:

*

The addressing mode is the addressing mode of the destination operand <EAd>.

Notes

For the @aa:8 access range, refer to the relevant microcontroller hardware manual.

C

∧

C

7

0

Specified by #xx:3

Bit No.

Invert

<EAd>

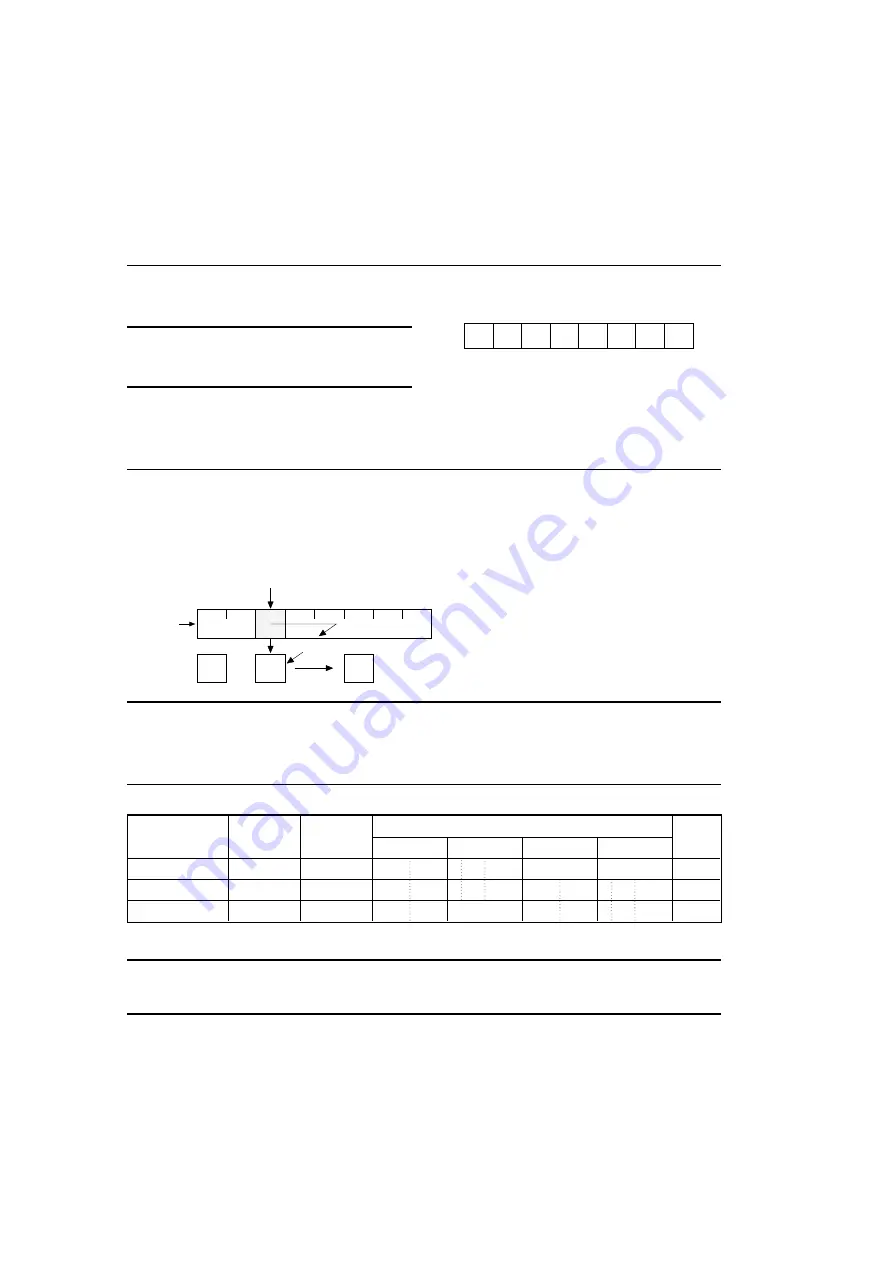

Instruction Format

1st byte

2nd byte

3rd byte

4th byte

Register direct

BIAND

#xx:3.Rd

7

6

1 IMM

rd

2

Register indirect

BIAND

#xx:3.@ERd

7

C

0 erd

0

7

6

1 IMM

0

6

Absolute address

BIAND

#xx:3.@aa:8

7

E

abs

7

6

1 IMM

0

6

No. of

States

Addressing

Mode

*

Mnemonic

Operands

56