2.9.9

IRQ Interrupts as FIQ Interrupt Sources

Interrupts from the IRQ interrupt can be placed on FIQ6 and FIQ7 können.

The interrupts of the FIQ interrupt controller are used for debugging, monitoring address area access, and for the

watchdog.

FIQ interrupts no. 4 and 5 are the interrupts for embedded ICE RT communication. The UART can also be used as a

debugger in place of the ICE. Effective real-time debugging is possible when the IRQ interrupt sources of the UART are

mapped to the FIQs with the number 6 or 7. This enables debugging of interrupt routines.

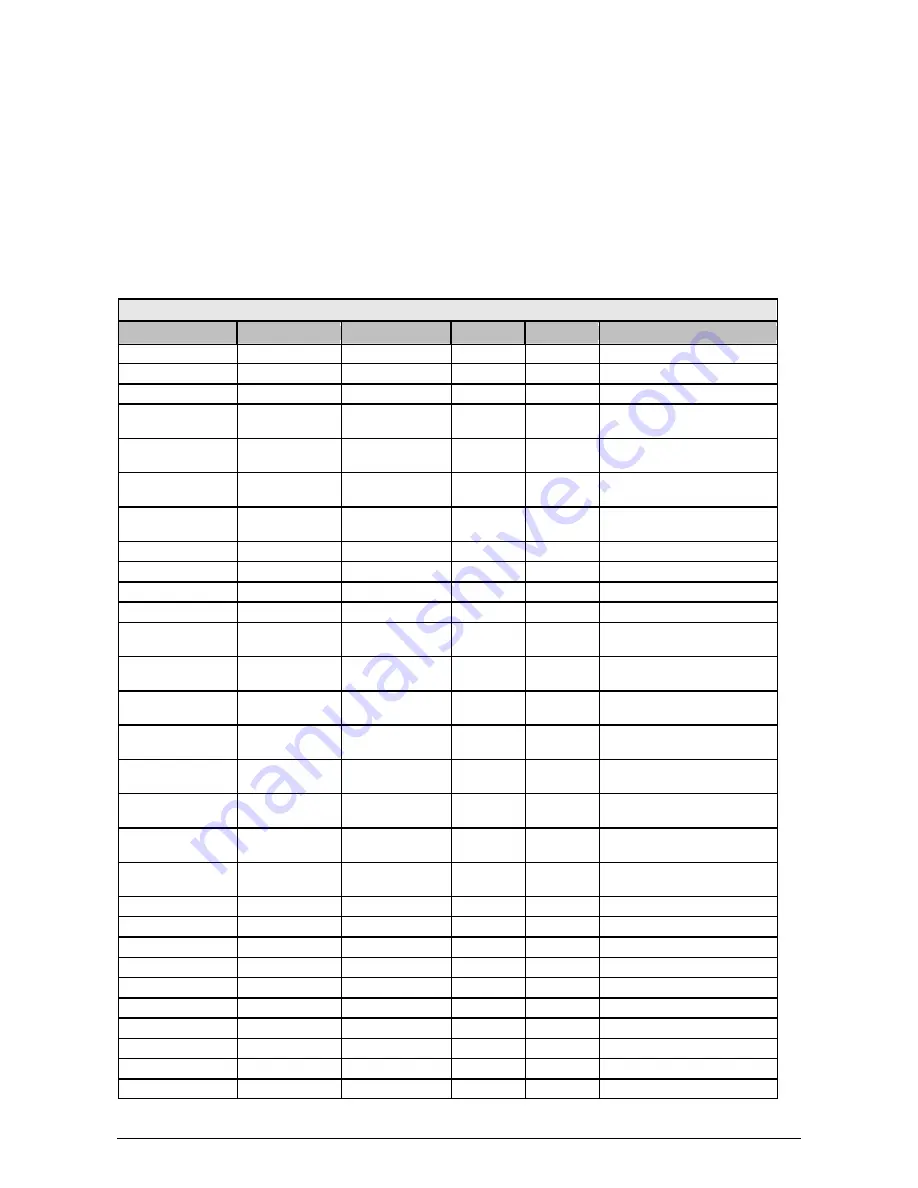

2.9.10 Interrupt Control Register

The interrupt control registers are used to specify all aspects of control, prioritization, and masking of the IRQ/FIQ

interrupt controllers.

ICU

(Base Address 0x5000_0000)

Register Name

Offset Address

Address Area

Access

Default

Description

IRVEC

0x0000 4

bytes

R

0xFFFFFFFF

Interrupt vector register

FIVEC

0x0004 4

bytes

R

0xFFFFFFFF

Fast interrupt vector register

LOCKREG

0x0008 4

bytes

R/W

0x00000000

Priority lock register

FIQ1SREG 0x000C 4

bytes

R/W

0x00000000

Fast int. request 1 select register

(FIQ6 on FIQ interrupt controller)

FIQ2SREG 0x0010 4

bytes

R/W

0x00000000

Fast int. request 2 select register

(FIQ7 on FIQ interrupt controller)

IRQACK

0x0014 4

bytes

R

0xFFFFFFFF

Interrupt vector register with IRQ

acknowledge

FIQACK

0x0018 4

bytes

R

0xFFFFFFFF

Fast interrupt vector register with

FIQ acknowledge

IRCLVEC

0x001C 4

bytes

W

0x----

Interrupt request clear vector

MASKALL

0x0020 4

bytes

R/W

0x00000001

Mask for all interrupts

IRQEND 0x0024 4

bytes

W

0x----

End of IRQ interrupt

FIQEND

0x0028 4

bytes

W

0x----

End of FIQ interrupt

FIQPR0

0x002C 4

bytes

R/W

0x00000007

FIQ priority register on input FIQ0

of the FIQ interrupt controller

FIQPR1 0x0030 4

bytes

R/W

0x00000007

FIQ priority register on input FIQ1

of the FIQ interrupt controller

FIQPR2

0x0034 4

bytes

R/W

0x00000007

FIQ priority register on input FIQ2

of the FIQ interrupt controller

FIQPR3 0x0038 4

bytes

R/W

0x00000007

FIQ priority register on input FIQ3

of the FIQ interrupt controller

FIQPR4 0x003C 4

bytes

R/W

0x00000007

FIQ priority register on input FIQ4

of the FIQ interrupt controller

FIQPR5 0x0040 4

bytes

R/W

0x00000007

FIQ priority register on input FIQ5

of the FIQ interrupt controller

FIQPR6 0x0044 4

bytes

R/W

0x00000007

FIQ priority register on input FIQ6

of the FIQ interrupt controller

FIQPR7 0x0048 4

bytes

R/W

0x00000007

FIQ priority register on input FIQ7

of the FIQ interrupt controller

FIQISR

0x004C 4

bytes

R

0x00000000

FIQ in-service register

FIQIRR

0x0050 4

bytes

R

0x00000020

FIQ request register

FIQ_MASKREG

0x0054 4

bytes

R/W

0x000000FF

FIQ interrupt mask register

IRREG

0x0058 4

bytes

R

0x000001xx

Interrupt request register

MASKREG

0x005C 4

bytes

R/W

0x0000FFFF

Interrupt mask register

ISREG

0x0060 4

bytes

R

0x00000000

In-service register

TRIGREG

0x0064 4

bytes

R/W

0x00000000

Trigger select register

EDGEREG

0x0068 4

bytes

R/W

0x00000000

Edge select register

SWIRREG

0x006C 4

bytes

R/W

0x00000000

Software interrupt register

PRIOREG 0

0x0070 4

bytes

R/W

0x0000000F

Priority register 0

Copyright © Siemens AG 2007. All rights reserved.

26

ERTEC 200 Manual

Technical data subject to change

Version 1.1.0