SiRFatlasV

Hardware Design Guide

January, 2010

SiRF Design Guide

– Proprietary and Confidential

13

Warm_RST_B(X_GPIO[8])

This pins default is

GPIO<8>

and is configured by the software as a warm reset, when input is

low, SoC logic will finish all warm reset procedures, DRAM will be set in self-refresh, and most of

the SoC logic will be reset except the RTC logic and power on/off control logic.

On_Key 15 second reset

When a user presses the On_key continuously for up to 15 seconds, the SoC will reset similar to

X-RTC_RST_B

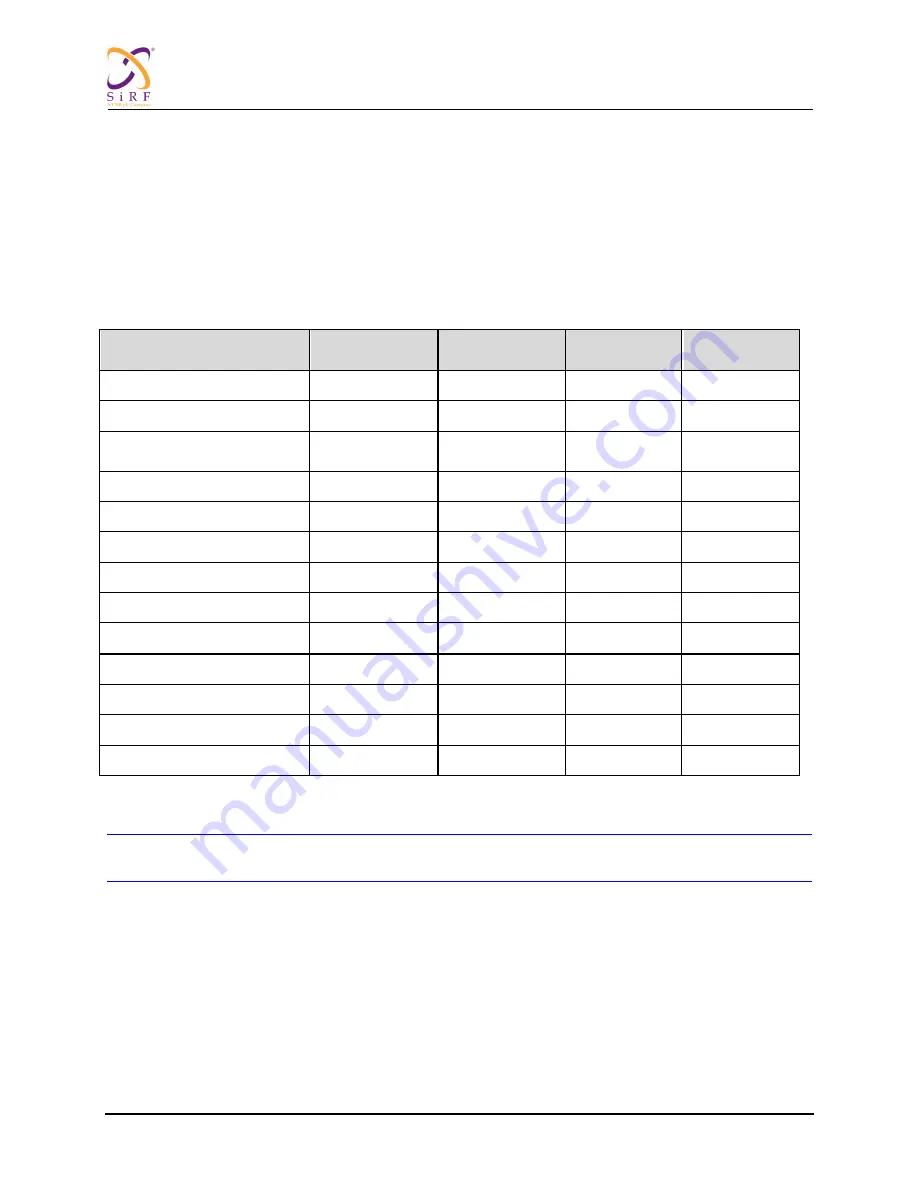

The following table describes the behavior of various types of reset.

Module

X_RTC_RST_B

On_Key 15s

X_RESET_B

Warm-reset

Power on/off control logic

Yes

Yes

No

No

GPSRTC

Power-off

Power-off

Yes

No

SYSRTC

Yes

Yes

No

No

RISC Core

Power-off

Power-off

Yes

Yes

RISC Interface

Power-off

Power-off

Yes

Yes

Interrupt Controller

Power-off

Power-off

Yes

Yes

CLKC

Power-off

Power-off

Yes

Yes

Timer

Power-off

Power-off

Yes

Yes

Reset controller

Power-off

Power-off

Yes

No

GPIO

Power-off

Power-off

Yes

Yes

System Arbiter

Power-off

Power-off

Yes

Yes

RISC CP14 Registers

Power-off

Power-off

Yes

No

Other SoC logic blocks

Power-off

Power-off

Yes

Yes

Table 4: Reset Behavior

NOTE

–

“Power-off” means the SoC logic will be powered off through x_system_en and x_dram_en as

“low”; “Yes” means the SoC power is supplied, the logic module is reset.

For details about the resets, refer to

CS-130805-DS SiRFatlasV Datasheet

.

If the GPS device has a reset button, it is recommended to use warm-reset or X_REST_B to connect to

this reset button. The following table shows the behavior when these four types of reset work as the reset

button.