SiRFatlasV

Hardware Design Guide

January, 2010

SiRF Design Guide

– Proprietary and Confidential

15

This issue happens during the four typical cases of I/O power loss:

When the system enters deep-sleep or hibernation mode

Before the SoC goes into deep-sleep mode or hibernation mode, the software needs to shutdown

peripherals

’ power to avoid the peripherals driving the SoC I/O pads and thus resulting in I/O

leakage when the I/O power is disabled.

When the system is running, the user randomly presses the On-Key for 15s or X_RTC_RST_B

These two reset issues happen randomly by end users but are not controlled by software. It may

result in serious system instability. For example:

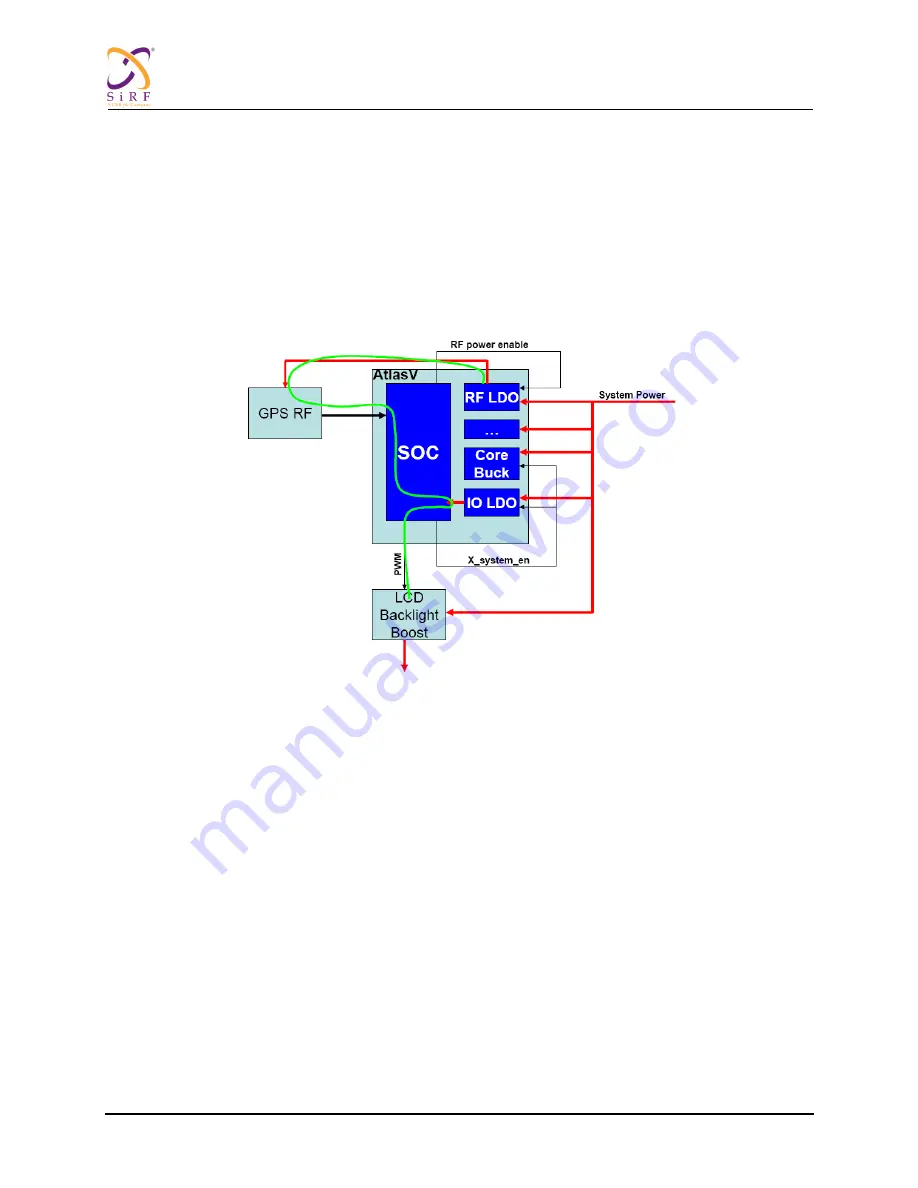

Figure 9: Random RTC Reset or On Key 15s Issue

When the system is running and the random RTC reset or On Key 15s issue happens, x_system_en and

x_dram_en will output low to disable most of the LDO and buck inside the PMU. However because the

software has no time to control the GPIO to disable the RF LDO, the RF LDO will keep working and the

RF chip will still be powered on. Thus the RF chip keeps driving signals to to the SoC

’s I/O pad through

the GPS BB signal pads and the pad

’s internal ESD circuit, leakage will go to the I/O VDD. Although the

I/O LDO is disabled, this leakage causes the I/O VDD to have a 1.xV~2.xV floating voltage, therefore the

RF LDO

’s enable signal and LCD backlight boost’s enable signal will also have a 1.xV~2.xV level signal.

The voltage may be above the RF LDO and LCD boost enable signal threshold, so these two regulators

keep working.

The I/O leakage due to the RF LDO issue is a dead-loop. The LCD backlight boost will result in a white-

screen and an uncomfortable user experience. Especially, when the system goes into this dead-loop

status, the end user can only remove the battery to recover the system.

To solve this problem, reset the SoC logic before the SoC

’s I/O and core power loss. Assume that on the

hardware design, the default status of the peripheral

’s enable signals such as RF power enable and LCD

backlight enable, after system power-on and reset

is “disabled”, when the random RTC reset or On key

15s issue happens, x_system_en or x_dram_en goes to low to disable most of the SoC regulators. If,

before the SoC I/O and core power are fully discharged, there is a way to pull X_RESET_B to low rapidly,