59

Control Registers

3

.

EEPROM Write Register 0 Bit Definitions

Bits 15 through 00:

EW0 [15...0] -

The lower 16 bits represent the number of times the

E

2

PROM has been written to in hexadecimal format.

Control and Status Register (Channel 0 Example)

This register contains information pertinent to Channel 0. Each channel has its own CSR,

which is identical in operation to the one described in Table 3-14 below. The bit definitions

are also shown below.

Powerup/Reset Default = $0807

Control and Status Register Bit Definitions

Bit 15:

Format -

This bit controls the format of the data written to the

RAM. A logical zero (0) returns offset binary format. A logical

one (1) returns two’s complement format. The default is offset

binary. This bit is ignored for unipolar ranges. For unipolar

ranges, the output is always binary.

Bit 14:

RTD -

This bit enables the RTD Excitation supply when set to a

logical one (1). The default condition is a logic zero (0).

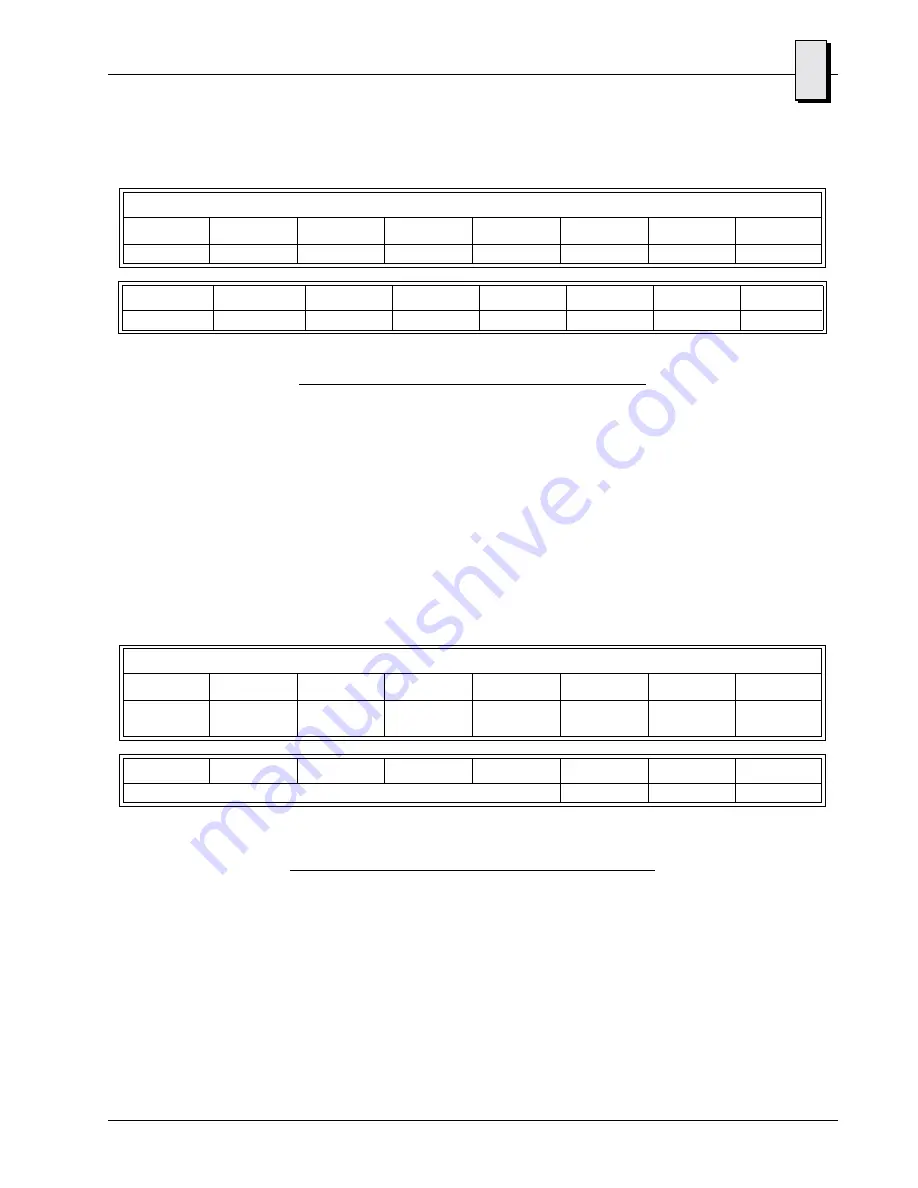

Table 3-13 EEPROM Writes Register 0’s Bit Map

EEPROM Writes Register 0 (Offset $0012) Read Only, Byte/Word

Bit 15

Bit 14

Bit 13

Bit 12

Bit 11

Bit 10

Bit 09

Bit 08

EW0_15

EW0_14

EW0_13

EW0_12

EW0_11

EW0_10

EW0_9

EW0_8

Bit 07

Bit 06

Bit 05

Bit 04

Bit 03

Bit 02

Bit 01

Bit 00

EW0_7

EW0_6

EW0_5

EW0_4

EW0_3

EW0_2

EW0_1

EW0_0

Table 3-14 Control and Status Register’s Bit Map

Channel 0 Control and Status Register (Offset $0020) Read/Write, Byte/Word

Bit 15

Bit 14

Bit 13

Bit 12

Bit 11

Bit 10

Bit 9

Bit 8

Format

RTD

Open

Sensor

Reserved

Range

Bit 3

Range

Bit 2

Range

Bit 1

Range

Bit 0

Bit 07

Bit 06

Bit 05

Bit 04

Bit 03

Bit 02

Bit 01

Bit 00

Reserved

FC2

FC1

FC0

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com