CMT2380F17

Rev0.1 | 312/347

www.cmostek.com

29 Page P SFR Access

CMT2380F17 builds a special SFR page (Page P) to store the control registers for MCU operation.

These SFRs can be accessed by the ISP/IAP operation with different IFMT. In page P access, IFADRH must

set to “00” and IFADRL indexes the SFR address in page P. If IFMT= 04H for Page P writing, the content in

IFD will be loaded to the SFR in IFADRL indexed after the SCMD triggered. If IFMT = 05H for Page P reading,

the content in IFD is stored the SFR value in IFADRL indexed after the SCMD triggered.

Following descriptions are the SFR function definition in Page P:

IAPLB

:

IAP Low Boundary

SFR Page

= P

SFR Address = 0x03

Bit

7

6

5

4

3

2

1

0

Name

IAPLB[7:0]

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Reset Value

1

1

1

1

1

1

1

0

Bit 7~0: The IAPLB determines the IAP-memory lower boundary. Since a Flash page has 512

bytes, the IAPLB must be an even number.

To read IAPLB, MCU need to define the IFADRL for SFR address in Page-P, the IFMT for mode

selection on Page-P Read and set ISPCR.ISPEN. And then write 0x46h & 0xB9h sequentially into

SCMD. The IAPLB content is available in IFD. If write IAPLB, MCU will put new IAPLB setting

value in IFD firstly. And index IFADRL, select IFMT, enable ISPCR.ISPEN and then set SCMD.

The IAPLB content has already finished the updated sequence.

The range of the IAP-memory is determined by IAPLB and the ISP Start address as listed below.

IAP lower boundary = IAPLBx256, and

IAP higher boundary = ISP start address

– 1.

For example, if IAPLB=0xE0 and ISP start address is 0xF000, then the IAP-memory range is

located at 0xE000 ~ 0xEFFF.

Additional attention point, the IAP low boundary address must not be higher than ISP start address.

CKCON2

:

Clock Control Register 2

SFR Page

= P Only

SFR Address = 0x40

Bit

7

6

5

4

3

2

1

0

Name

--

--

--

IHRCOE

MCKS1

MCKS0

OSCS1

OSCS0

R/W

W

W

W

R/W

R/W

R/W

R/W

R/W

Reset Value

0

0

0

1

0

0

0

0

Bit 4: IHRCOE, Internal High frequency RC Oscillator Enable. 0: Disable internal high frequency RC

oscillator.

1: Enable internal high frequency RC oscillator. If this bit is set by CPU software, it needs 32 us to have

stable output after IHRCOE is enabled.

Bit 3~2: MCKS[1:0], MCK Source Selection.

。

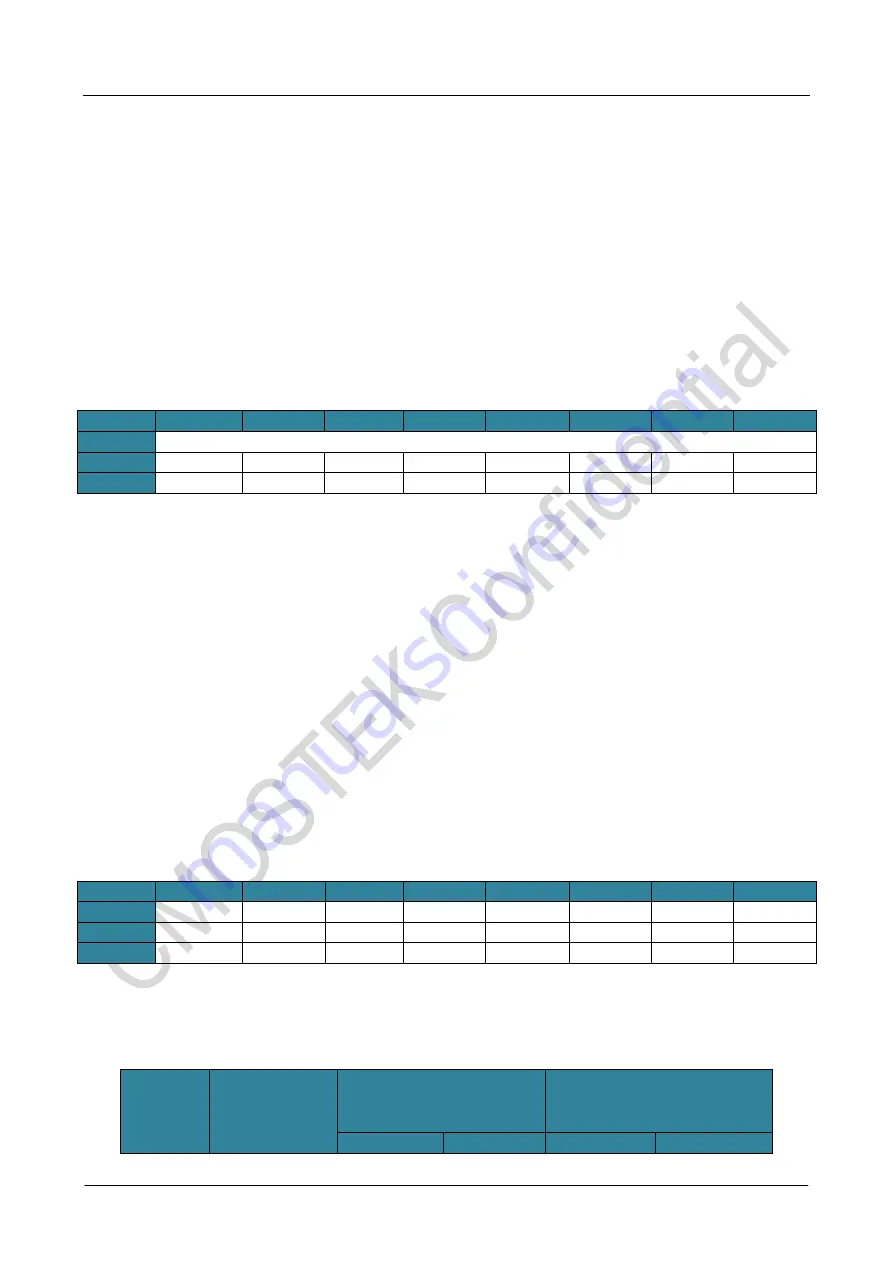

MCKS[1:0] MCK

时钟源选择

OSCin =12MHz

CKMIS = [01]

OSCin =11.059MHz

CKMIS = [01]

CKMS0=0

CKMS0=1

CKMS0=0

CKMS0=1

Summary of Contents for CMT2380F17

Page 27: ...CMT2380F17 Rev0 1 27 347 www cmostek com 1 25 Phase Noise...

Page 177: ...CMT2380F17 Rev0 1 177 347 www cmostek com Figure 17 3 PCA Interrupt System...

Page 246: ...CMT2380F17 Rev0 1 246 347 www cmostek com SnMIPS S0MI S1MI 1 P3 3 P4 7...