CMT2380F17

Rev0.1 | 48/347

www.cmostek.com

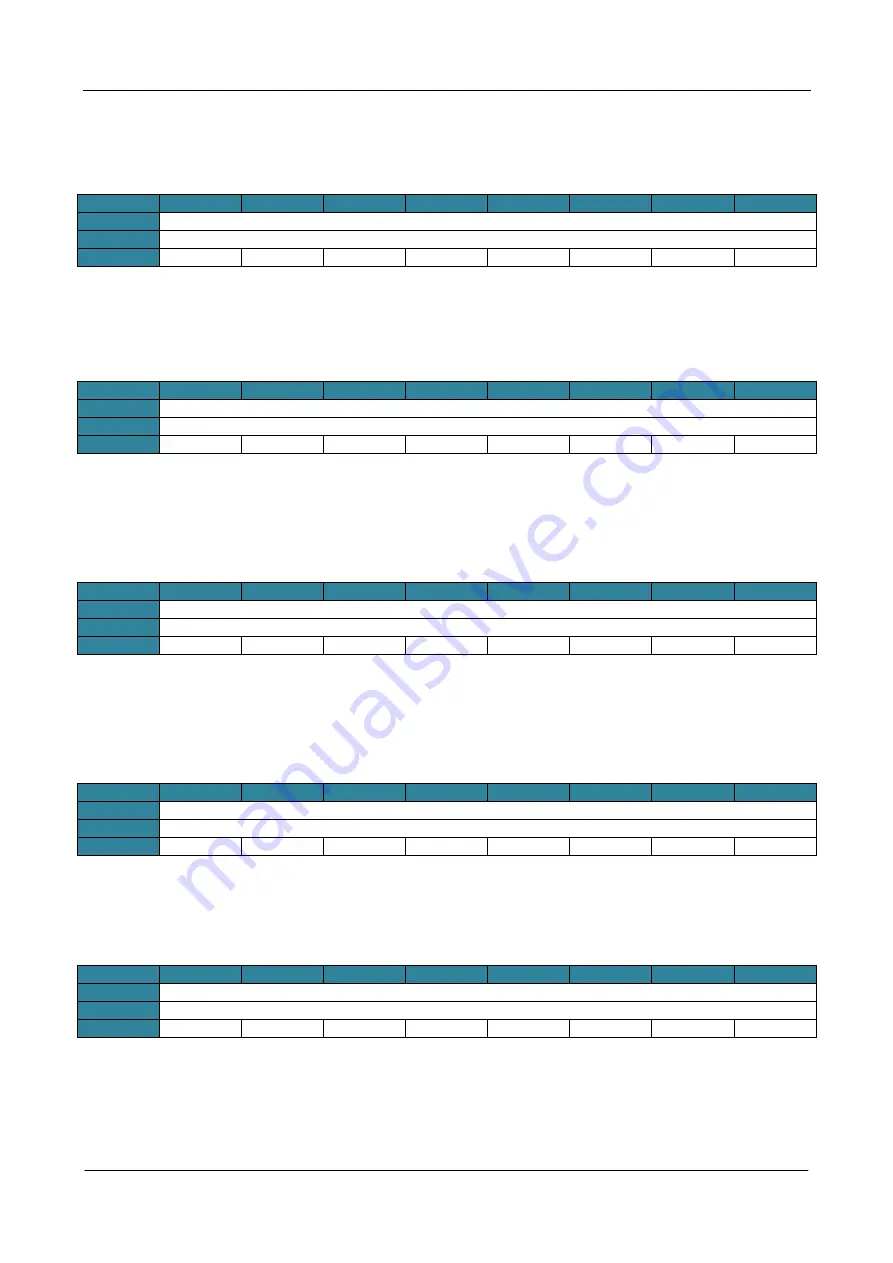

SP

: Stack Pointer

SFR Page

= 0~F

SFR Address = 0x81

Bit

7

6

5

4

3

2

1

0

Name

SP[7:0]

R/W

R/W

Reset Value

0

0

0

0

0

1

1

1

The Stack Pointer holds the location of the top of the stack. The stack pointer is incremented before every

PUSH operation. The SP register defaults to 0x07 after reset.

DPL

: Data Pointer Low

SFR Page

= 0~F

SFR Address = 0x82

Bit

7

6

5

4

3

2

1

0

Name

DPTR[7:0]

R/W

R/W

Reset Value

0

0

0

0

0

0

0

0

The DPL register is the low byte of the 16-bit DPTR. DPTR is used to access indirectly addressed XRAM

and Flash memory.

DPH

: Data Pointer High

SFR Page

= 0~F

SFR Address = 0x83

Bit

7

6

5

4

3

2

1

0

Name

DPTR[15:8]

R/W

R/W

Reset Value

0

0

0

0

0

0

0

0

The DPH register is the high byte of the 16-bit DPTR. DPTR is used to access indirectly addressed

XRAM and Flash memory.

ACC

: Accumulator

SFR Page

= 0~F

SFR Address = 0xF0

Bit

7

6

5

4

3

2

1

0

Name

ACC[7:0]

R/W

R/W

Reset Value

0

0

0

0

0

0

0

0

This register is the accumulator for arithmetic operations.

B: B

Register

SFR Page

= 0~F

SFR Address = 0xF0

Bit

7

6

5

4

3

2

1

0

Name

B[7:0]

R/W

R/W

Reset Value

0

0

0

0

0

0

0

0

This register serves as a second accumulator for certain arithmetic operations.

5.2

CPU Timing

CMT2380F17 is a single-chip microcontroller based on a high performance 1-T architecture 80C51 CPU

that has an 8051 compatible instruction set, and executes instructions in 1~7 clock cycles (about 6~7 times

Summary of Contents for CMT2380F17

Page 27: ...CMT2380F17 Rev0 1 27 347 www cmostek com 1 25 Phase Noise...

Page 177: ...CMT2380F17 Rev0 1 177 347 www cmostek com Figure 17 3 PCA Interrupt System...

Page 246: ...CMT2380F17 Rev0 1 246 347 www cmostek com SnMIPS S0MI S1MI 1 P3 3 P4 7...