Rev. 2.10

206

���� 02� 201�

Rev. 2.10

207

���� 02� 201�

HT68F20/HT68F30/HT68F40/HT68F50/HT68F60

HT68FU30/HT68FU40/HT68FU50/HT68FU60

Enhanced I/O Flash Type 8-Bit MCU with EEPROM

HT68F20/HT68F30/HT68F40/HT68F50/HT68F60

HT68FU30/HT68FU40/HT68FU50/HT68FU60

Enhanced I/O Flash Type 8-Bit MCU with EEPROM

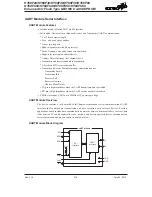

Serial Interface Module Interrupt

The Serial Interface Module Interrupt, also known as the SIM interrupt, is contained within the

Multi-function Interrupt. A SIM Interrupt request will take place when the SIM Interrupt request

flag, SIMF, is set, which occurs when a byte of data has been received or transmitted by the SIM

interface. To allow the program to branch to its respective interrupt vector address, the global

interrupt enable bit, EMI, and the Serial Interface Interrupt enable bit, SIME, and Muti-function

interrupt enable bits, must first be set. When the interrupt is enabled, the stack is not full and a byte

of data has been transmitted or received by the SIM interface, a subroutine call to the respective

Multi-function Interrupt vector, will take place. When the Serial Interface Interrupt is serviced, the

EMI bit will be automatically cleared to disable other interrupts, however only the Multi-function

interrupt request flag will be also automatically cleared. As the SIMF flag will not be automatically

cleared, it has to be cleared by the application program.

External Peripheral Interrupt

The External Peripheral Interrupt operates in a similar way to the external interrupt and is contained

within the Multi-function Interrupt. A Peripheral Interrupt request will take place when the External

Peripheral Interrupt request flag, XPF, is set, which occurs when a negative edge transition appears

on the PINT pin. To allow the program to branch to its respective interrupt vector address, the

global interrupt enable bit, EMI, external peripheral interrupt enable bit, XPE, and associated

Multi-function interrupt enable bit, must first be set. When the interrupt is enabled, the stack is not

full and a negative transition appears on the External Peripheral Interrupt pin, a subroutine call to

the respective Multi-function Interrupt, will take place. When the External Peripheral Interrupt is

serviced, the EMI bit will be automatically cleared to disable other interrupts, however only the

Multi-function interrupt request flag will be also automatically cleared.

As the XPF flag will not be automatically cleared, it has to be cleared by the application program.

The external peripheral interrupt pin is pin-shared with several other pins with different functions. It

must therefore be properly configured to enable it to operate as an External Peripheral Interrupt pin.

EEPROM Interrupt

The EEPROM Interrupt, is contained within the Multi-function Interrupt. An EEPROM Interrupt

request will take place when the EEPROM Interrupt request flag, DEF, is set, which occurs when an

EEPROM Write or Read cycle ends. To allow the program to branch to its respective interrupt vector

address, the global interrupt enable bit, EMI, EEPROM Interrupt enable bit, DEE, and associated

Multi-function interrupt enable bit, must first be set. When the interrupt is enabled, the stack is not

full and an EEPROM Write or Read cycle ends, a subroutine call to the respective Multi-function

Interrupt vector, will take place. When the EEPROM Interrupt is serviced, the EMI bit will be

automatically cleared to disable other interrupts, however only the Multi-function interrupt request

flag will be also automatically cleared. As the DEF flag will not be automatically cleared, it has to be

cleared by the application program.