CPU12

INSTRUCTION GLOSSARY

MOTOROLA

REFERENCE MANUAL

6-49

Operation:

(SP) – $0002

⇒

SP

RTN

H

: RTN

L

⇒

M

(SP)

: M

(SP

+

1)

(PC)

+

Rel

⇒

PC

Description:

Sets up conditions to return to normal program flow, then transfers con-

trol to a subroutine. Uses the address of the instruction after the BSR as

a return address.

Decrements the SP by two, to allow the two bytes of the return ad-

dress to be stacked.

Stacks the return address (the SP points to the high order byte of the

return address).

Branches to a location determined by the branch offset.

Subroutines are normally terminated with an RTS instruction, which re-

stores the return address from the stack.

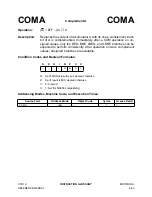

Condition Codes and Boolean Formulas:

None affected.

Addressing Modes, Machine Code, and Execution Times:

BSR

Branch to Subroutine

BSR

S

X

H

I

N

Z

V

C

–

–

–

–

–

–

–

–

Source Form

Address Mode

Object Code

Cycles

Access Detail

BSR

rel8

REL

07 rr

4

PPPS

Summary of Contents for CPU12

Page 8: ...MOTOROLA CPU12 viii REFERENCE MANUAL ...

Page 14: ...MOTOROLA INTRODUCTION CPU12 1 4 REFERENCE MANUAL ...

Page 20: ...MOTOROLA OVERVIEW CPU12 2 6 REFERENCE MANUAL ...

Page 38: ...MOTOROLA INSTRUCTION QUEUE CPU12 4 6 REFERENCE MANUAL ...

Page 300: ...MOTOROLA DEVELOPMENT AND DEBUG SUPPORT CPU12 8 16 REFERENCE MANUAL ...

Page 338: ...MOTOROLA MEMORY EXPANSION CPU12 10 8 REFERENCE MANUAL ...

Page 364: ...MOTOROLA INSTRUCTION REFERENCE CPU12 A 26 REFERENCE MANUAL ...

Page 386: ...MOTOROLA HIGH LEVEL LANGUAGE SUPPORT CPU12 C 6 REFERENCE MANUAL ...

Page 438: ...MOTOROLA SUMMARY OF CHANGES CPU12 S 2 REFERENCE MANUAL ...

Page 439: ......