CPU12

HIGH-LEVEL LANGUAGE SUPPORT

MOTOROLA

REFERENCE MANUAL

C-5

The CPU12 has dedicated signal lines that allow the CPU to access the bank page

register without having to use an address in the normal 64-Kbyte address space. This

eliminates the need for the program to know where the page register is physically lo-

cated.

The RTC instruction is similar to the RTS instruction, except that RTC uses the byte

of information that was saved on the stack by the corresponding CALL instruction to

restore the bank page register to its old value. Although a CALL/RTC pair can be used

to access any function subroutine regardless of the location of the called routine (on

the current bank page or a different page), it is most efficient to access some subrou-

tines with JSR/RTS instructions when the called subroutine is on the current page or

in an area of memory that is always visible in the 64-Kbyte map regardless of the bank

page selection.

Push and pull instructions can be used to stack some or all the CPU registers during

a function call. The CPU12 can push and pull any of the CPU registers A, B, CCR, D,

X, Y, or SP.

C.9 Instruction Set Orthogonality

One very helpful aspect of the CPU12 instruction set, orthogonality, is difficult to quan-

tify in terms of direct benefit to an HLL compiler. Orthogonality refers to the regularity

of the instruction set. A completely orthogonal instruction set would allow any instruc-

tion to operate in any addressing mode, would have identical code sizes and execution

times for similar operations on different registers, and would include both signed and

unsigned versions of all mathematical instructions. Greater regularity of the instruction

makes it possible to implement compilers more efficiently, because operation is more

consistent, and fewer special cases must be handled.

Summary of Contents for CPU12

Page 8: ...MOTOROLA CPU12 viii REFERENCE MANUAL ...

Page 14: ...MOTOROLA INTRODUCTION CPU12 1 4 REFERENCE MANUAL ...

Page 20: ...MOTOROLA OVERVIEW CPU12 2 6 REFERENCE MANUAL ...

Page 38: ...MOTOROLA INSTRUCTION QUEUE CPU12 4 6 REFERENCE MANUAL ...

Page 300: ...MOTOROLA DEVELOPMENT AND DEBUG SUPPORT CPU12 8 16 REFERENCE MANUAL ...

Page 338: ...MOTOROLA MEMORY EXPANSION CPU12 10 8 REFERENCE MANUAL ...

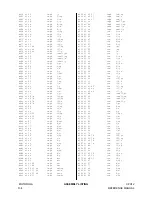

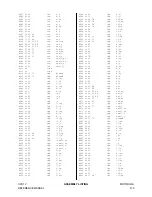

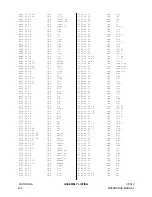

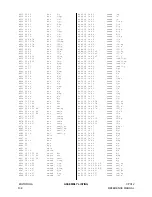

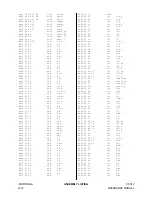

Page 364: ...MOTOROLA INSTRUCTION REFERENCE CPU12 A 26 REFERENCE MANUAL ...

Page 386: ...MOTOROLA HIGH LEVEL LANGUAGE SUPPORT CPU12 C 6 REFERENCE MANUAL ...

Page 438: ...MOTOROLA SUMMARY OF CHANGES CPU12 S 2 REFERENCE MANUAL ...

Page 439: ......