CPU12

MOTOROLA

REFERENCE MANUAL

I-1

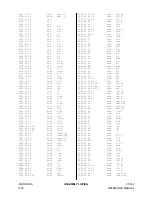

INDEX

A

A 2-1, 3-5, 5-8, 6-8, 6-11, 6-13, 6-15 to 6-16,

B 2-1, 3-5, 5-8, 6-8 to 6-10, 6-12, 6-14 to 6-15,

D 2-1, 3-5, 5-8, 6-15, 6-22, 6-65, 6-70 to 6-71,

Direct 3-3

Extended 3-3

Immediate 3-2

Indexed 2-2, 3-5

Inherent 3-2

Memory expansion 10-7

Relative 3-4

B

Background debugging mode 5-22, 8-6

BKGD pin 8-7 to 8-9

Commands 8-9 to 8-10

Enabling and disabling 8-6

Instruction 5-22, 6-31, 8-6

Registers 8-11

ROM 8-6

Serial interface 8-7 to 8-9

Bit manipulation instructions 5-7, 6-27, 6-48, B-15,

Mask operand 3-11, 6-27, 6-48

Multiple addressing modes 3-11, 6-27, 6-48

Bit test instructions 5-7, 6-35 to 6-36, C-1

BITA instruction 6-35

BITB instruction 6-36

Bit-condition branches 5-16, 6-45, 6-47

BKGD pin 8-7 to 8-9

BLE instruction 6-37

BLO instruction 6-38

BLS instruction 6-39

BLT instruction 6-40

BMI instruction 6-41

BNE instruction 6-42

Boolean logic instructions 5-6

BPL instruction 6-43

BRA instruction 6-44

Branch instructions 3-4, 4-4 to 4-5, 5-13, C-4

Bit-condition 4-4 to 4-5, 5-16, 6-45, 6-47

Long 4-4 to 4-5, 5-13, 6-104 to 6-121, B-13

INDEX

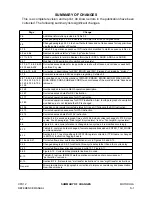

Summary of Contents for CPU12

Page 8: ...MOTOROLA CPU12 viii REFERENCE MANUAL ...

Page 14: ...MOTOROLA INTRODUCTION CPU12 1 4 REFERENCE MANUAL ...

Page 20: ...MOTOROLA OVERVIEW CPU12 2 6 REFERENCE MANUAL ...

Page 38: ...MOTOROLA INSTRUCTION QUEUE CPU12 4 6 REFERENCE MANUAL ...

Page 300: ...MOTOROLA DEVELOPMENT AND DEBUG SUPPORT CPU12 8 16 REFERENCE MANUAL ...

Page 338: ...MOTOROLA MEMORY EXPANSION CPU12 10 8 REFERENCE MANUAL ...

Page 364: ...MOTOROLA INSTRUCTION REFERENCE CPU12 A 26 REFERENCE MANUAL ...

Page 386: ...MOTOROLA HIGH LEVEL LANGUAGE SUPPORT CPU12 C 6 REFERENCE MANUAL ...

Page 438: ...MOTOROLA SUMMARY OF CHANGES CPU12 S 2 REFERENCE MANUAL ...

Page 439: ......