Nations Technologies Inc.

Tel

:

+86-755-86309900

:

info@nationstech.com

Address: Nations Tower, #109 Baoshen Road, Hi-tech Park North.

Nanshan District, Shenzhen, 518057, P.R.China

295

/

631

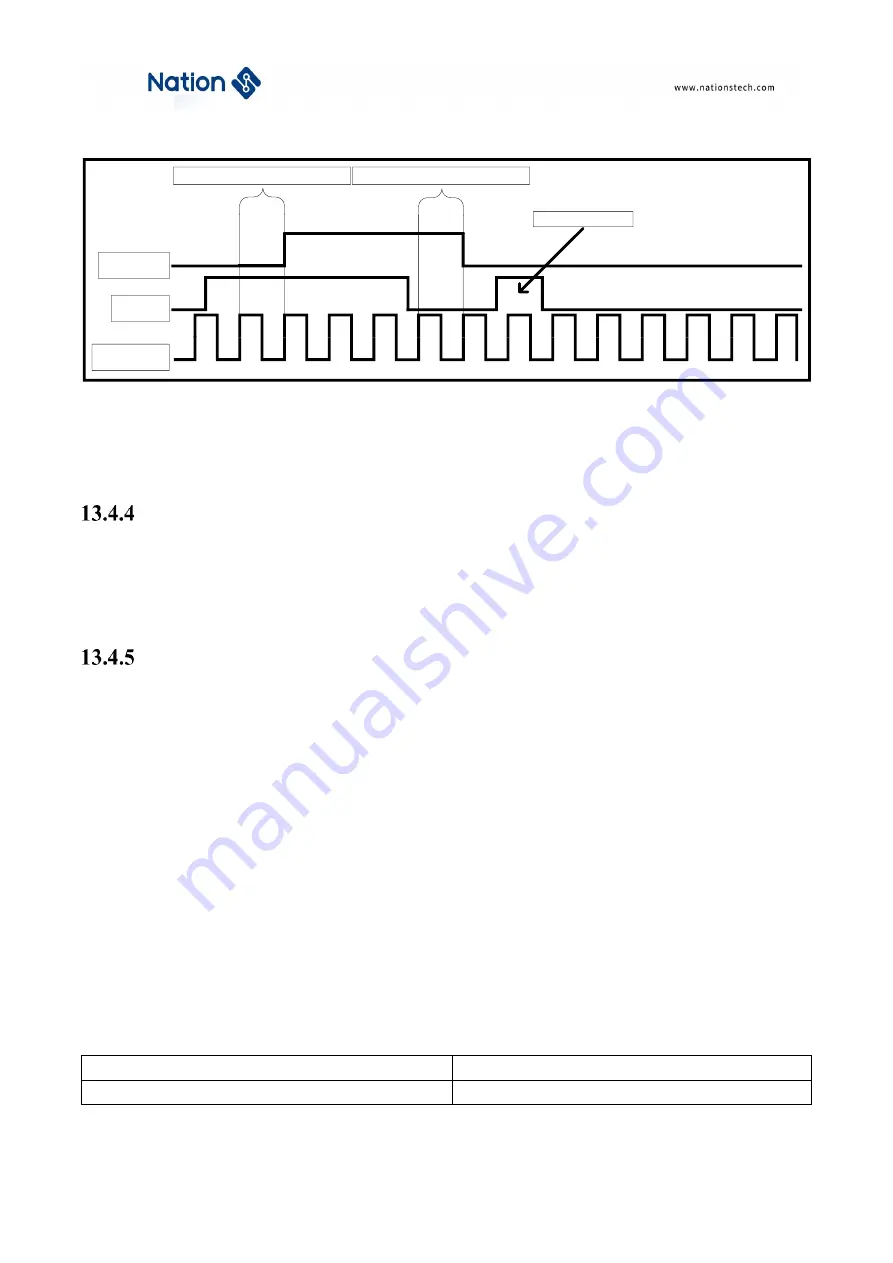

Figure 13-2 Glitch filter timing diagram

Note: If no internal clock is used, the glitch filter needs to be turned off by clearing LPTIM_CFG.CLKFLT[1:0]

and LPTIM_CFG.TRIGFLT[1:0] bits. If glitch filter is not used, the user can use a digital filter in the comparator

or an external analog filter to remove the glitch.

Timer enable

The LPTIM_CTRL.LPTIMEN bit is used to enable/disable the LPTIM kernel logic. After setting the

LPTIM_CTRL.LPTIMEN bit, a delay of two counter clock is needed before the LPTIM is turned on.

The LPTIM_CFG and LPTIM_INTEN registers must be modified only when the LPTIM is turned off.

Trigger multiplexer

The LPTIM counter can be triggered either by software or by an active edge on one of the 8 trigger inputs.

The trigger source is configured through LPTIM_CFG.TRGEN[1:0] bits. LPTIM_CFG.TRGEN[1:0] = ‘00’, the

trigger is selected as LPTIM_CTRL.TSTCM or LPTIM_CTRL.SNGMST bit, which can be set by software. The

other values of LPTIM_CFG.TRGEN[1:0] are for the active edge configuration of the trigger. The internal counter

will start once an active edge is detected.

LPTIM_CFG.TRGSEL[2:0] is used to select one of the 8 trigger inputs only when LPTIM_CFG.TRGEN[1:0] is not

equal to ‘00’.

If LPTIM is using external trigger, which will be considered as asynchronous triggers. For asynchronous triggers,

the LPTIM needs two counter clock cycles latency for synchronization.

If timeout function is disabled, new trigger event will be ignored if the LPTIM is already started.

Note: Any write to the LPTIM_CTRL.SNGMST/ LPTIM_CTRL.TSTCM bit will be discarded if the LPTIM is not

enabled.

Table 13-2 9 trigger inputs corresponding to LPTIM_CFG.TRGSEL[2:0] bits

Control bits

Corresponding trigger input

000

PB6 or PC3

2 consecutive samples

2 consecutive samples

Filtered

Input

CLKMUX

Filter out