7.4.3 Comparator Mode

All the DAC channels can be configured as programmable comparators in the voltage-output mode. To enter

the comparator mode for a channel, write 1 to the CMP-X-EN bit in the respective DAC-X-VOUT-CMP-CONFIG

register. The comparator output can be configured as push-pull or open-drain using the CMP-X-OD-EN bit. To

enable the comparator output on the output pin, write 1 to the CMP-X-OUT-EN bit. To invert the comparator

output, write 1 to the CMP-X-INV-EN bit. The FBx pin has a finite impedance. By default, the FBx pin is in the

high-impedance mode. To disable high-impedance on the FBx pin, write 1 to the CMP-X-HIZ-IN-DIS bit.

shows the comparator output at the pin for different bit settings.

Note

In the Hi-Z input mode, the comparator input range is limited to:

• For GAIN = 1x, 1.5x, or 2x: V

FB

≤ (V

REF

× GAIN) / 3

• For GAIN = 3x, or 4x: V

FB

≤ (V

REF

× GAIN) / 6

Any higher input voltage is clipped.

Table 7-1. Comparator Output Configuration

CMP-X-EN

CMP-X-OUT-EN

CMP-X-OD-EN

CMP-X-INV-EN

CMPX-OUT PIN

0

X

X

X

Comparator not enabled

1

0

X

X

No output

1

1

0

0

Push-pull output

1

1

0

1

Push-pull and inverted output

1

1

1

0

Open-drain output

1

1

1

1

Open-drain and inverted output

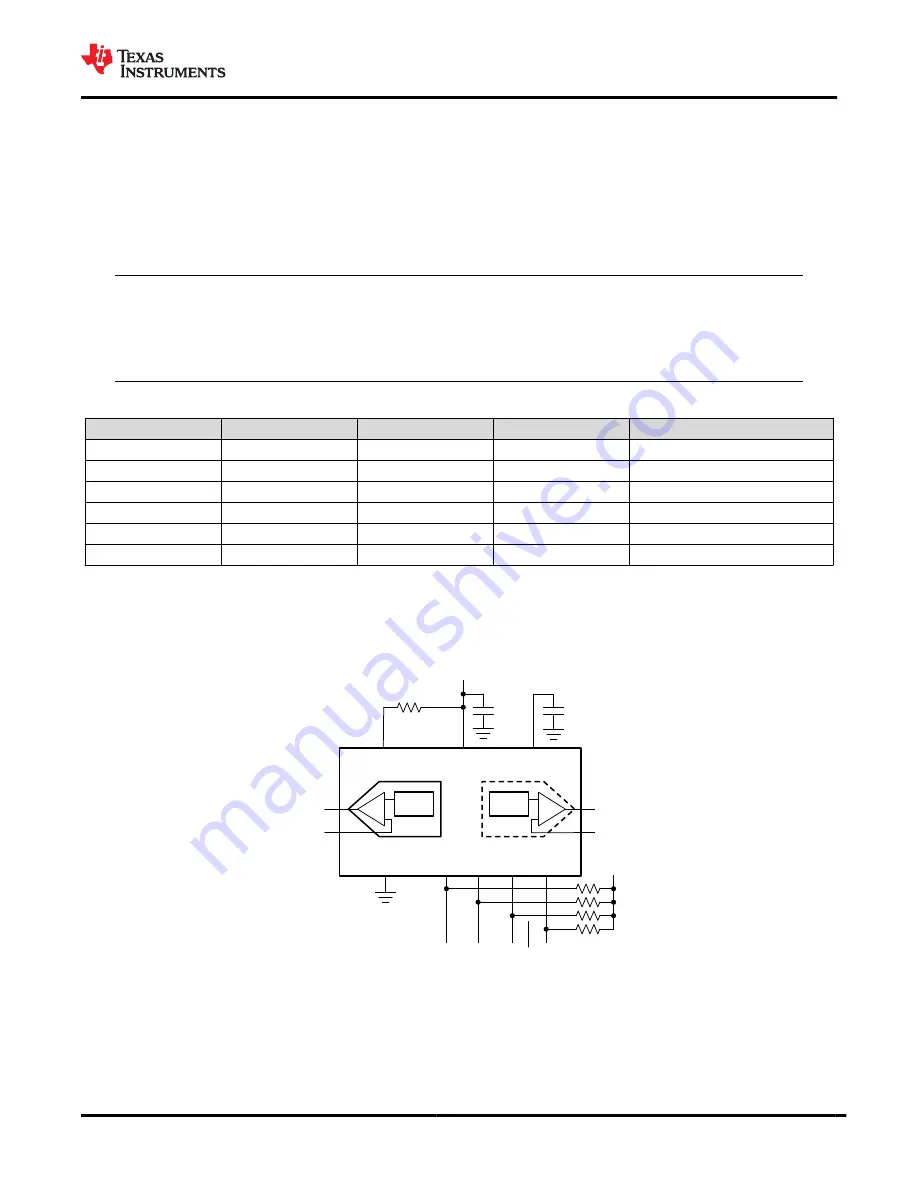

shows the interface circuit when all the DAC channels are configured as comparators. The

programmable comparator operation is as shown in

. Individual comparator channels can be

configured in no-hysteresis, with-hysteresis, and window-comparator modes using the CMP-X-MODE bit in the

respective DAC-X-CMP-MODE-CONFIG register, as shown in

A0/SDI

GPIO/SDO

VDD

SCL/SY

NC

SDA/S

CLK

AGND

0.1

μ

F

1.5

μ

F

CAP

VDD

VREF

10 k

+

-

CMP0

+

-

CMP1

FB1/AIN1

VIO

10 k

(0 V to V

FS

/3 or 0 V to V

FS

)

(0 V to V

FS

/3 or 0 V to V

FS

)

FB0/AIN0

CMP0-OUT

CMP1-OUT

Figure 7-3. Comparator Interface

DAC53001, DAC53002, DAC63001, DAC63002

SLASF48 – MAY 2022

Copyright © 2022 Texas Instruments Incorporated

31

Product Folder Links: