7.4.5 Application-Specific Modes

This section provides the details of application-specific functional modes available in the DACx300x.

7.4.5.1 Voltage Margining and Scaling

Voltage margining or scaling is a primary application for the DACx300x. This section provides specific features

available for this application such as Hi-Z output, slew-rate control, PROTECT input, and PMBus compatibility.

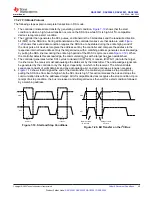

7.4.5.1.1 High-Impedance Output and PROTECT Input

All the DAC output channels remain in a high-impedance state (Hi-Z) when VDD is off.

simplified schematic of the DACx300x used in a voltage-margining application. Series resistor R

S

is required in

voltage-output mode, but is optional in current-output mode. Almost all linear regulators and DC/DC converters

have a feedback voltage of ≤ 1.25 V. The low-leakage currents at the outputs are maintained for V

FB

of ≤

1.25 V. Thus, for all practical purposes, the DAC outputs appear as Hi-Z when VDD of the DAC is off in voltage

margining and scaling applications. This feature allows for seamless integration of the DACx300x into a system

without any need for additional power-supply sequencing for the DAC.

DAC

V

IN

V

REG

R

1

R

2

R

S

V

FB

Linear

Regulator

or

DC/DC

Converter

VDD

1.25 V

Z

OUT

I

LEAK

PROTECT

Figure 7-9. High-Impedance (Hi-Z) Output and PROTECT Input

The DAC channels power down to Hi-Z at boot up. The outputs can power up with a preprogrammed code that

corresponds to the nominal output of the DC/DC converter or the linear regulator. This feature allows for smooth

power up and power down of the DAC without impacting the feedback loop of the DC/DC converter or the linear

regulator.

shows how the GPIO pin of the DACx300x can be configured as a PROTECT function. PROTECT

takes the DAC outputs to a predictable state with a slewed or direct transition. This function is useful in systems

where a fault condition (such as a brownout), a subsystem failure, or a software crash requires that the DAC

outputs reach a predefined state without the involvement of a processor. The detected event can be fed to

the GPIO pin that is configured as the PROTECT input. The PROTECT function can also be triggered using

the PROTECT bit in the COMMON-TRIGGER register.

shows how to configure the behavior of the

PROTECT function in the PROTECT-CONFIG field in the DEVICE-MODE-CONFIG register.

Note

• After the PROTECT function is triggered, the write functionality is disabled on the communication

interface until the function is completed.

• The PROTECT-FLAG bit in the CMP-STATUS register is set to 1 when the PROTECT function

is triggered. This bit can be polled by reading the CMP-STATUS register. After the PROTECT

function is complete, a read command on the CMP-STATUS register resets the PROTECT-FLAG

bit.

Table 7-4. PROTECT Function Configuration

PROTECT-CONFIG FIELD

FUNCTION

00

Switch to Hi-Z power-down (no slew).

01

Switch to DAC code stored in NVM (no slew) and then switch to Hi-Z power-down.

10

Slew to margin-low code and then switch to Hi-Z power-down.

11

Slew to margin-high code and then switch to Hi-Z power-down.

DAC53001, DAC53002, DAC63001, DAC63002

SLASF48 – MAY 2022

36

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: