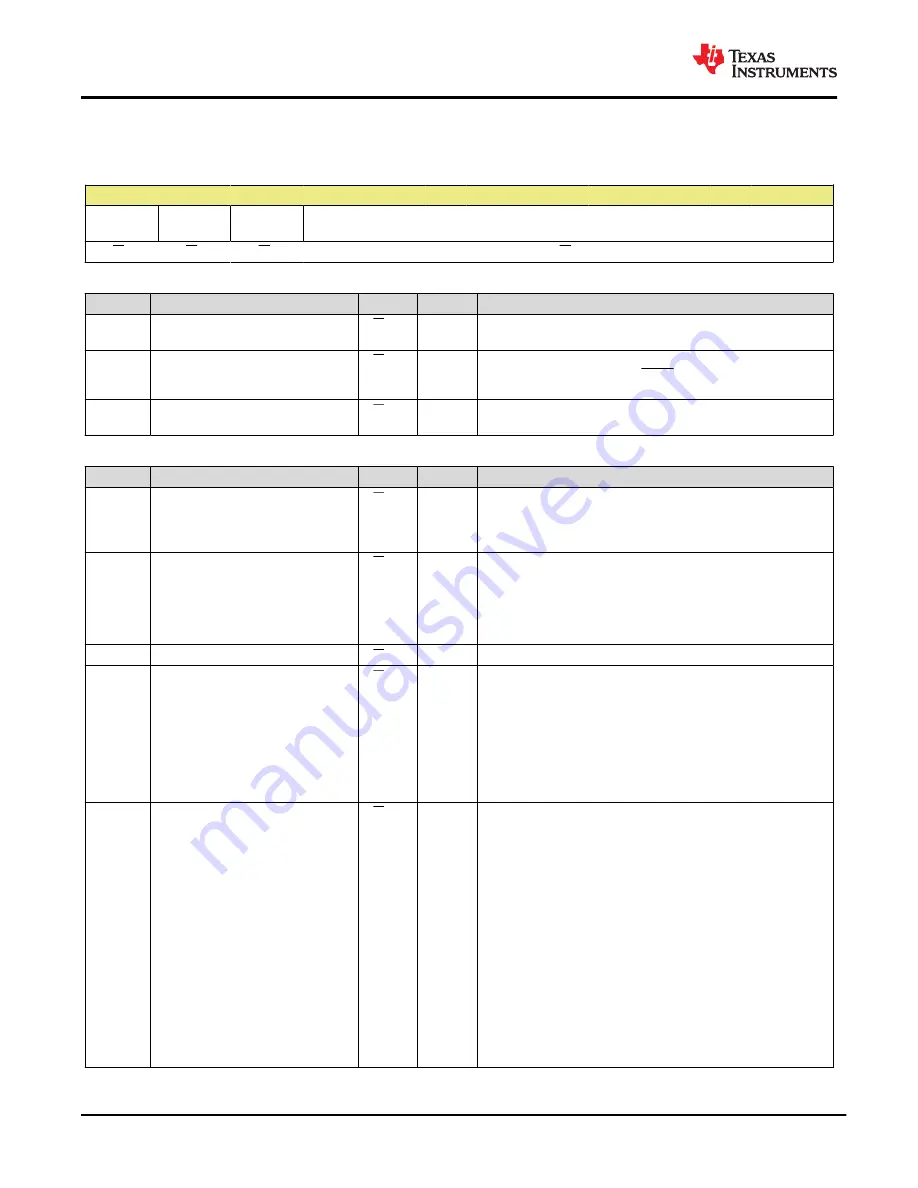

7.6.7 DAC-X-FUNC-CONFIG Register (address = 18h, 06h) [reset = 0000h]

PMBus page address = FFh, PMBus register address = E0h, D4h

Figure 7-28. DAC-X-FUNC-CONFIG Register (X = 0, 1)

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

CLR-SEL-X

SYNC-

CONFIG-X

BRD-

CONFIG-X

FUNC-GEN-CONFIG-BLOCK

R/W-0h

R/W-0h

R/W-0h

R/W-0h

Table 7-29. DAC-X-FUNC-CONFIG Register Field Descriptions

Bit

Field

Type

Reset

Description

15

CLR-SEL-X

R/W

0

0: Clear DAC-X to zero-scale

1: Clear DAC-X to mid-scale

14

SYNC-CONFIG-X

R/W

0

0: DAC-X output updates immediately after a write command

1: DAC-X output updates with LDAC pin falling-edge or when the

LDAC bit in the COMMON-TRIGGER register is set to 1

13

BRD-CONFIG-X

R/W

0

0: Don't update DAC-X with broadcast command

1: Update DAC-X with broadcast command

Table 7-30. Linear-Slew Mode: FUNC-GEN-CONFIG-BLOCK Field Descriptions

Bit

Field

Type

Reset

Description

12-11

PHASE-SEL-X

R/W

0

00: 0°

01: 120°

10: 240°

11: 90°

10-8

FUNC-CONFIG-X

R/W

0

000: Triangular wave

001: Sawtooth wave

010: Inverse sawtooth wave

100: Sine wave

111: Disable function generation

Others: Invalid

7

LOG-SLEW-EN-X

R/W

0

0: Enable linear slew

6-4

CODE-STEP-X

R/W

0

CODE-STEP for linear slew mode:

000: 1-LSB

001: 2-LSB

010: 3-LSB

011: 4-LSB

100: 6-LSB

101: 8-LSB

110: 16-LSB

111: 32-LSB

3-0

SLEW-RATE-X

R/W

0

SLEW-RATE for linear slew mode:

0000: No slew for margin-high and margin-low. Invalid for

waveform generation.

0001: 4 µs/step

0010: 8 µs/step

0011: 12 µs/step

0100: 18 µs/step

0101: 27.04 µs/step

0110: 40.48 µs/step

0111: 60.72 µs/step

1000: 91.12 µs/step

1001: 136.72 µs/step

1010: 239.2 µs/step

1011: 418.64 µs/step

1100: 732.56 µs/step

1101: 1282 µs/step

1110: 2563.96 µs/step

1111: 5127.92 µs/step

DAC53001, DAC53002, DAC63001, DAC63002

SLASF48 – MAY 2022

60

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: