7.5 Programming

The DACx300x are programmed through either a 3-wire SPI or 2-wire I

2

C interface. A 4-wire SPI mode is

enabled by mapping the GPIO pin as SDO. The SPI readback operates at a lower SCLK than the standard

SPI write operation. The type of interface is determined based on the first protocol to communicate after device

power up. After the interface type is determined, the device ignores any change in the type while the device is

on. The interface type can be changed after a power cycle.

7.5.1 SPI Programming Mode

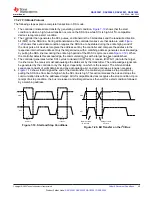

An SPI access cycle for DACx300x is initiated by asserting the SYNC pin low. The serial clock, SCLK, can be

a continuous or gated clock. SDI data are clocked on SCLK falling edges. The SPI frame for DACx300x is 24

bits long. Therefore, the SYNC pin must stay low for at least 24 SCLK falling edges. The access cycle ends

when the SYNC pin is deasserted high. If the access cycle contains less than the minimum clock edges, the

communication is ignored. By default, the SDO pin is not enabled (three-wire SPI). In the three-wire SPI mode,

if the access cycle contains more than the minimum clock edges, only the first 24 bits are used by the device.

When SYNC is high, the SCLK and SDI signals are blocked, and SDO becomes Hi-Z to allow data readback

from other devices connected on the bus.

describe the format for the 24-bit SPI access cycle. The first byte input to SDI is the

instruction cycle. The instruction cycle identifies the request as a read or write command and the 7-bit address

that is to be accessed. The last 16 bits in the cycle form the data cycle.

Table 7-12. SPI Read/Write Access Cycle

BIT

FIELD

DESCRIPTION

23

R/W

Identifies the communication as a read or write command to the address register: R/W = 0 sets a write

operation. R/W = 1 sets a read operation

22-16

A[6:0]

Register address: specifies the register to be accessed during the read or write operation

15-0

DI[15:0]

Data cycle bits: If a write command, the data cycle bits are the values to be written to the register with

address A[6:0]. If a read command, the data cycle bits are

don't care

values.

1

24

8

9

D23

D16

D15

D0

Write command

SYNC

SCLK

SDI

SDO

1

24

8

9

D23

D16

D15

D0

Any command

D23

D16

D15

D0

HiZ

HiZ

HiZ

Write command echo

Figure 7-14. SPI Write Cycle

Read operations require that the SDO pin is first enabled by setting the SDO-EN bit in the INTERFACE-CONFIG

register. This configuration is called four-wire SPI. A read operation is initiated by issuing a read command

access cycle. After the read command, a second access cycle must be issued to get the requested data.

and

show the output data format. Data are clocked out on the SDO pin either on the falling

edge or rising edge of SCLK according to the FSDO bit (see also

Table 7-13. SDO Output Access Cycle

BIT

FIELD

DESCRIPTION

23

R/W

Echo R/W from previous access cycle

22-16

A[6:0]

Echo register address from previous access cycle

15-0

DI[15:0]

Readback data requested on previous access cycle

DAC53001, DAC53002, DAC63001, DAC63002

SLASF48 – MAY 2022

46

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: