Coprocessor Interface

7-10

Copyright © ARM Limited 2000. All rights reserved.

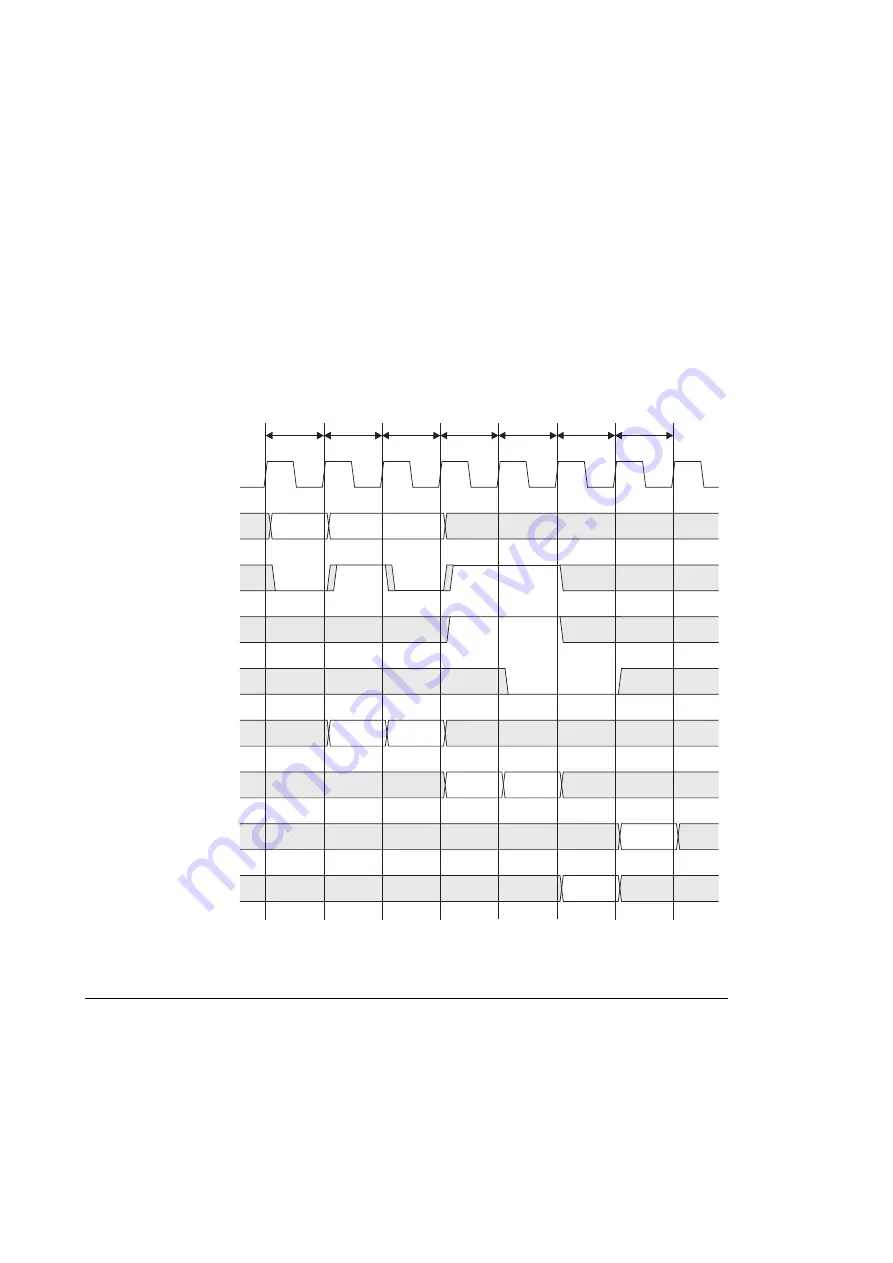

7.4

Interlocked MCR

If the data for an

MCR

operation is not available inside the ARM9E-S core pipeline

during its first Decode cycle, then the ARM9E-S core pipeline interlocks for one or

more cycles until the data is available. An example of this is where the register being

transferred is the destination from a preceding

LDR

instruction.

In this situation the

MCR

instruction enters the Decode stage of the coprocessor pipeline,

and then remains there for a number of cycles before entering the Execute stage.

Figure 7-4 gives an example of an interlocked

MCR

that also has a busy-wait state.

Figure 7-4 Interlocked MCR/MRC timing with busy-wait

LAST

Ignored

WAIT

CLK

nCPMREQ

CPINSTR[31:0]

CHSDE[1:0]

CHSEX[1:0]

CPDOUT[31:0]

MCR

CPPASS

CPLATECANCEL

MCR/

MRC

CPDIN[31:0]

MRC

Decode

(interlock)

Decode

Execute

(WAIT)

Execute

(LAST)

Memory

Coprocessor

pipeline

WAIT

Write

Fetch

Summary of Contents for ARM946E-S

Page 1: ...ARM DDI 0155A ARM946E S Technical Reference Manual ...

Page 6: ...vi Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A 04 Limited Confidential ...

Page 54: ...Programmer s Model 2 34 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Page 70: ...Caches 3 16 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Page 78: ...Protection Unit 4 8 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...

Page 112: ...Coprocessor Interface 7 14 Copyright ARM Limited 2000 All rights reserved ARM DDI 0155A ...