INTERRUPTS

11-19

11

11.7.2

Interrupt Detection Options

The XINT[7:0] pins can be programmed for level-low or falling-edge detection when used as

dedicated inputs. All dedicated inputs plus the NMI pin are programmed (globally) for fast

sampling or debounce sampling. Expanded-mode inputs are always sampled in debounce mode.

Pin detection and sampling options are selected by programming the ICON register.

When falling-edge detection is enabled and a high-to-low transition is detected, the processor sets

the corresponding pending bit in the IPND register. The processor clears the IPND bit upon entry

into the interrupt handler.

When a pin is programmed for low-level detection, the pin’s bit in the IPND register remains set as

long as the pin is asserted (low). The processor attempts to clear the IPND bit on entry into the

interrupt handler; however, if the active level on the pin is not removed at this time, the bit in the

IPND register remains set until the source of the interrupt is deactivated and the IPND bit is

explicitly cleared by software. Software may attempt to clear an interrupt pending bit before the

active level on the corresponding pin is removed. In this case, the active level on the interrupt pin

causes the pending bit to remain asserted.

After the interrupt signal is deasserted, the handler then clears the interrupt pending bit for that

source before return from handler is executed. If the pending bit is not cleared, the interrupt is

re-entered after the return is executed.

Example 11-5

demonstrates how a level detect interrupt is typically handled. The example assumes

that the

ld

from address “INTR_SRC,” deactivates the interrupt input.

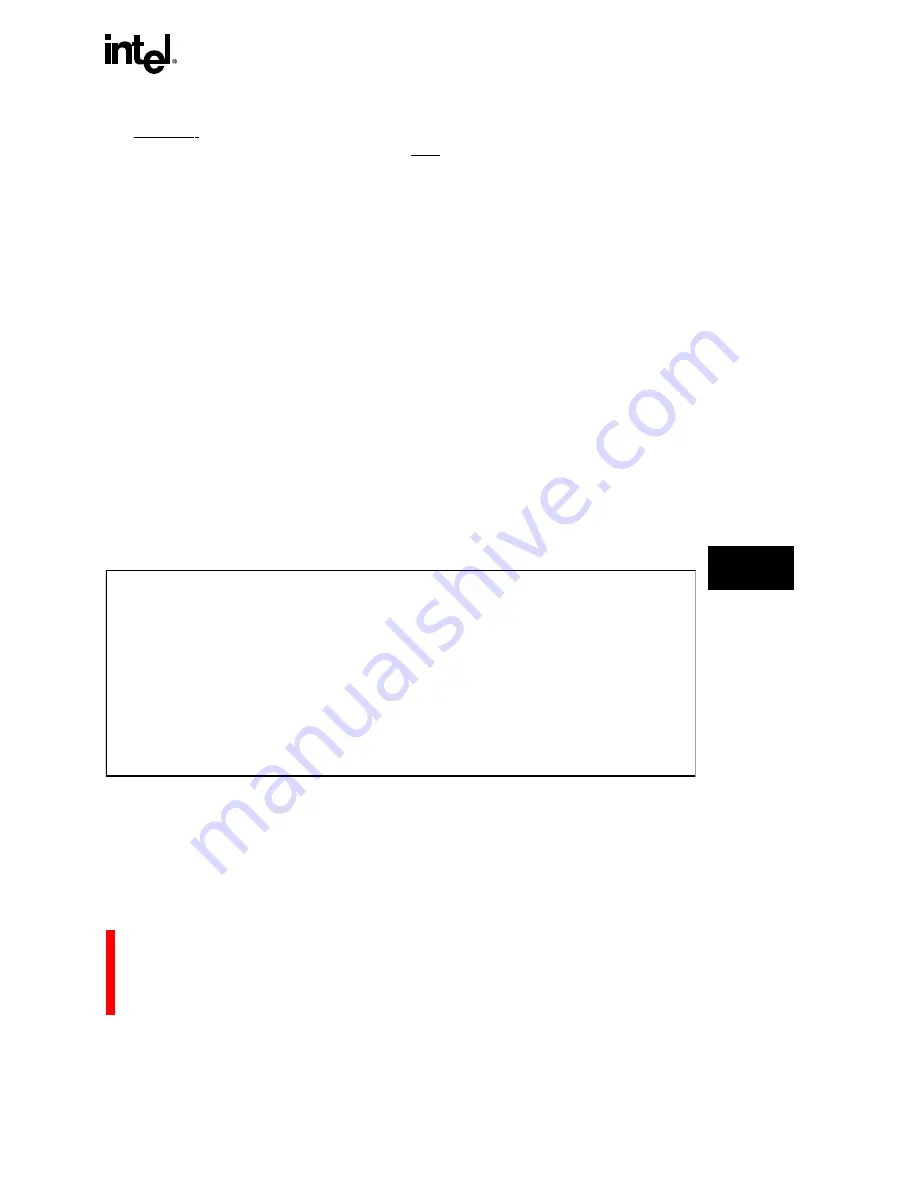

Example 11-5. Return from a Level-detect Interrupt

The debounce sampling mode provides a built-in filter for noisy or slow-falling inputs. The

debounce sampling mode requires that a low level is stable for three consecutive cycles before the

expanded mode vector is resolved internally. Expanded mode interrupts are always sampled using

the debounce sampling mode. This allows for skew time between changing outputs of external

priority encoders.

# Clear level-detect interrupts before return from handler

ld

INTR_SRC, g0 # Dismiss the extern. interrupt

lda

IPND_MMR, g1 # g1 = IPND MMR address

lda

0x80, g2

# g2 = mask to clear XINT7 IPND bit

# Loop until IPND bit 7 clears

wait:

mov

0,g3

# Try to clear the XINT7 IPND bit

atmod

g1, g2, g3

bbs

0x7, g3, wait# Branch until IPND bit 7 clears

# Optionally restore IMSK

mov

r3, IMSK

ret

# Return from handler

Summary of Contents for i960 Jx

Page 1: ...Release Date December 1997 Order Number 272483 002 i960 Jx Microprocessor Developer s Manual ...

Page 24: ......

Page 25: ...1 INTRODUCTION ...

Page 26: ......

Page 35: ...2 DATA TYPES AND MEMORY ADDRESSING MODES ...

Page 36: ......

Page 46: ......

Page 47: ...3 PROGRAMMING ENVIRONMENT ...

Page 48: ......

Page 73: ...4 CACHE AND ON CHIP DATA RAM ...

Page 74: ......

Page 85: ...5 INSTRUCTION SET OVERVIEW ...

Page 86: ......

Page 111: ...6 INSTRUCTION SET REFERENCE ...

Page 112: ......

Page 233: ...7 PROCEDURE CALLS ...

Page 234: ......

Page 256: ......

Page 257: ...8 FAULTS ...

Page 258: ......

Page 291: ...9 TRACING AND DEBUGGING ...

Page 292: ......

Page 309: ...10 TIMERS ...

Page 310: ......

Page 324: ......

Page 325: ...11 INTERRUPTS ...

Page 326: ......

Page 369: ...12 INITIALIZATION AND SYSTEM REQUIREMENTS ...

Page 370: ......

Page 412: ......

Page 413: ...13 MEMORY CONFIGURATION ...

Page 414: ......

Page 429: ...14 EXTERNAL BUS ...

Page 430: ......

Page 468: ......

Page 469: ...15 TEST FEATURES ...

Page 470: ......

Page 493: ...A CONSIDERATIONS FOR WRITING PORTABLE CODE ...

Page 494: ......

Page 502: ......

Page 503: ...B OPCODES AND EXECUTION TIMES ...

Page 504: ......

Page 515: ...C MACHINE LEVEL INSTRUCTION FORMATS ...

Page 516: ......

Page 523: ...D REGISTER AND DATA STRUCTURES ...

Page 524: ......

Page 550: ......

Page 551: ...GLOSSARY ...

Page 552: ......

Page 561: ...INDEX ...

Page 562: ......

Page 578: ......