1-7

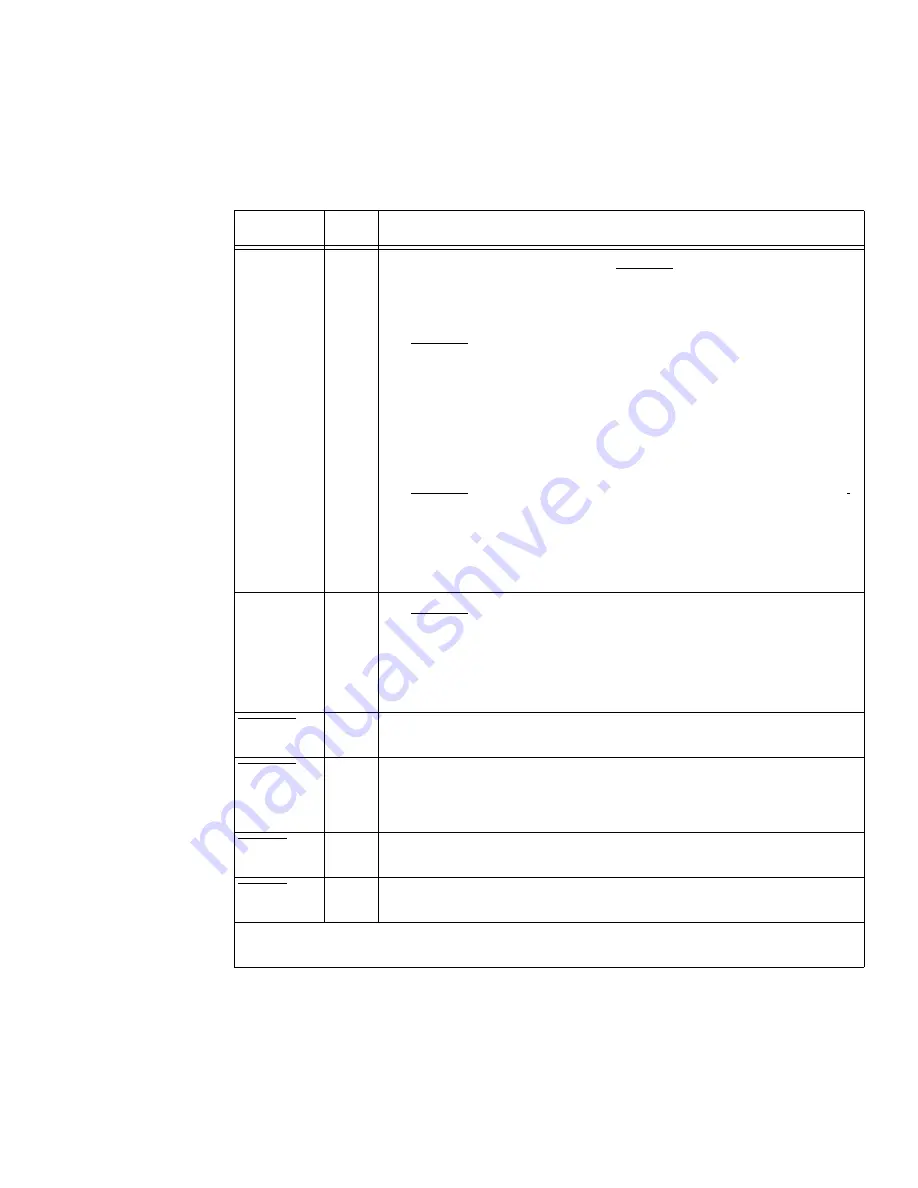

Reset, Configuration, and EOnCE Event Signals

BTM[0–1]

EE4

1

EE5

1

Input

Input

Output

Input

Output

Boot Mode 0–1

Determines the MSC8101 boot mode when PORESET is deasserted.

See the

Emulation

and Debug

chapter in the

SC140 DSP Core Reference Manual

for details on how to set

these pins.

EOnCE Event 4

After PORESET is deasserted, you can configure EE4 as an input (default) or an output.

See the

Emulation and Debug

chapter in the

SC140 DSP Core Reference Manual

for

details on the ETRSMT Register.

Enable Address Event Detection Channel 4 or generate one of the EOnCE events

EOnCE Transmit Register (ETRSMT) was written by the DSP. Used to trigger external

debugging equipment.

EOnCE Event 5

After PORESET is deasserted, you can configure EE5 as an input (default) or an output.

Enable Address Event Detection Channel 5.

Detection by Address Event Detection Channel 5. Used to trigger external debugging

equipment.

EED

1

Input

Output

Enhanced OnCE (EOnCE) Event Detection

After PORESET is deasserted, you can configure EED as an input (default) or output:

Enable the Data Event Detection Channel.

Detection by the Data Event Detection Channel. Used to trigger external debugging

equipment.

PORESET

Input

Power-On Reset

When asserted, this line causes the MSC8101 to enter power-on reset state.

RSTCONF

Input

Reset Configuration

Used during reset configuration sequence of the chip. A detailed explanation of its function

is provided in the “Power-On Reset Flow” and “Hardware Reset Configuration” sections of

the

MSC8101 Reference Manual

.

HRESET

Input

Hard Reset

When asserted, this open-drain line causes the MSC8101 to enter hard reset state.

SRESET

Input

Soft Reset

When asserted, this open-drain line causes the MSC8101 to enter soft reset state.

Note:

See the

Emulation and Debug

chapter in the

SC140 DSP Core Reference Manual

for details on how to

configure these pins.

Table 1-3. Reset, Configuration, and EOnCE Event Signals (Continued)

Signal Name

Type

Signal Description