6–42

Chapter 6: IP Core Interfaces

LMI Signals

Stratix V Hard IP for PCI Express

June 2012

Altera Corporation

lists the signals that indicate parity errors. When an error is detected,

parity error signals are asserted for one cycle.

LMI Signals

LMI interface is used to write log error descriptor information in the TLP header log

registers. The LMI access to other registers is intended for debugging, not normal

operation.

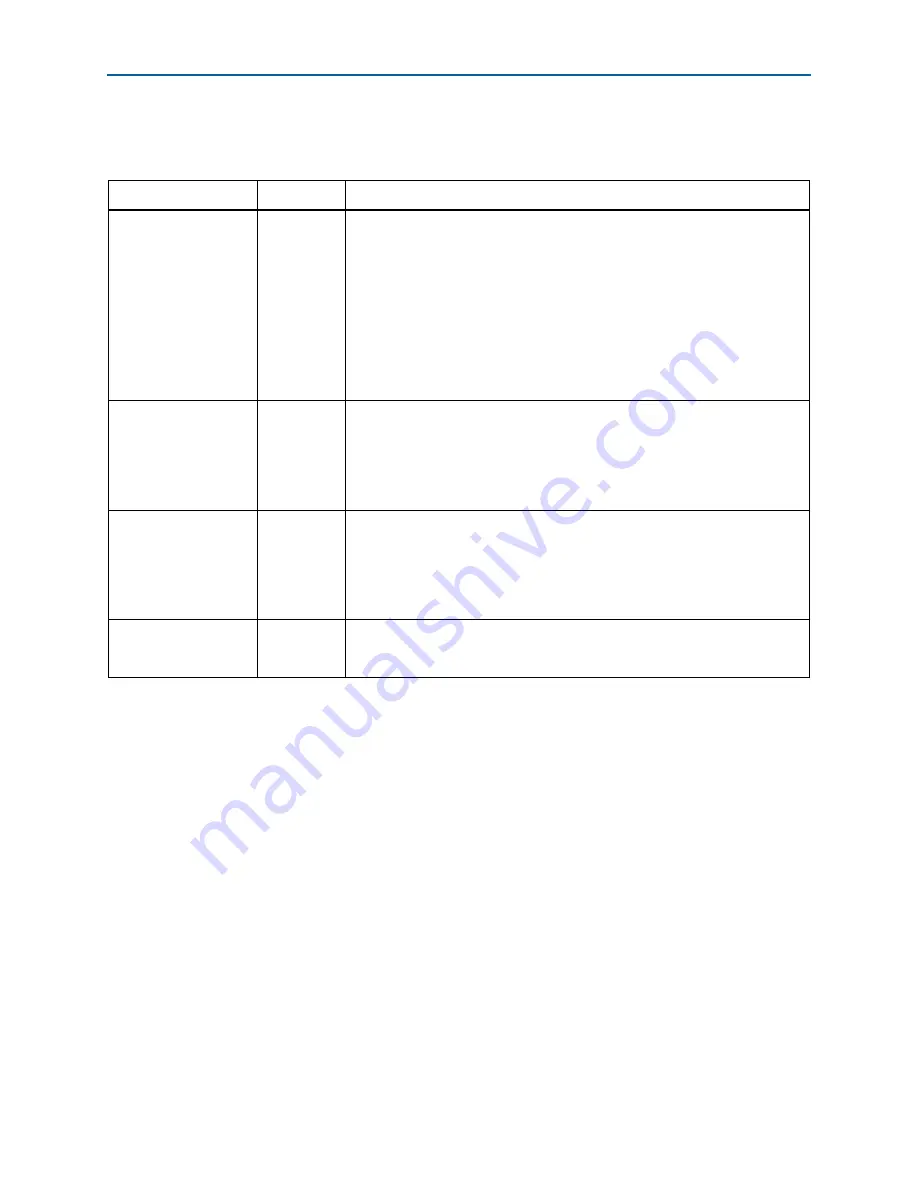

Table 6–18. Parity Signals

Signal Name

Direction

Description

tx_par_err[1:0]

O

When asserted for a single cycle, indicates a parity error during TX TLP

transmission. These errors are logged in the VSEC register. The following

encodings are defined:

■

2’b01: A parity error was detected by the TX Data Link Layer. Altera

recommends resetting the Stratix V Hard IP for PCI Express when this error is

detected. Contact Altera if resetting becomes unworkable.

■

2’b10: A parity error was detected by the TX Transaction Layer. The TLP is

nullified and logged as an uncorrectable internal error in the VSEC registers.

For more information, refer to

“Uncorrectable Internal Error Status Register”

.

rx_par_err

O

When asserted for a single cycle, indicates that a parity error was detected in a

TLP at the input of the RX buffer. This error is logged as an uncorrectable internal

error in the VSEC registers. For more information, refer to

Internal Error Status Register” on page 7–9

. If this error occurs, you must reset

the Hard IP if this error occurs because parity errors can leave the Hard IP in an

unknown state.

cfg_par_err

O

When asserted for a single cycle, indicates that a parity error was detected in a

TLP that was routed to internal Configuration Space or to the Configuration

Space Shadow Extension Bus. This error is logged as an uncorrectable internal

error in the VSEC registers. For more information, refer to

Internal Error Status Register” on page 7–9

. If this error occurs, you must reset

the core because parity errors can put the Hard IP in an unknown state.

cfg_par_err

O

Indicates that a parity error in a TLP routed to the internal Configuration Space.

This error is also logged in the Vendor Specific Extended Capability internal error

register. You must reset the Hard IP if this event occurs.