Chapter 5: IP Core Architecture

5–15

PCI Express Avalon-MM Bridge

June 2012

Altera Corporation

Stratix V Hard IP for PCI Express

PCI Express-to-Avalon-MM Downstream Read Requests

The PCI Express Avalon-MM bridge sends PCI Express read packets to the

interconnect fabric as burst reads with a maximum burst size of 512 bytes. The bridge

converts the PCI Express address to the Avalon-MM address space based on the BAR

hit information and address translation lookup table values. You can set up the

Address Translation Table Configuration using the parameter editor. Unsupported

read requests generate a completer abort response.

Avalon-MM-to-PCI Express Read Completions

The PCI Express Avalon-MM bridge converts read response data from Application

Layer Avalon-MM slaves to PCI Express completion packets and sends them to the

Transaction Layer.

A single read request may produce multiple completion packets based on the

Maximum payload size

and the size of the received read request. For example, if the

read is 512 bytes but the

Maximum payload size

128 bytes, the bridge produces four

completion packets of 128 bytes each. The bridge does not generate out-of-order

completions. You can specify the

Maximum payload size

parameter on the

Device

tab under the

PCI Express/PCI Capabilities

heading in the parameter editor. Refer to

“PCI Express and PCI Capabilities Parameters” on page 4–6

.

PCI Express-to-Avalon-MM Address Translation

The PCI Express Avalon-MM Bridge translates the system-level physical addresses,

typically up to 64 bits, to the 32-bit byte addresses used by the Application Layer. You

can specify up to six BARs for address translation when you customize your Hard IP

for PCI Express as described in

“Base Address Register (BAR) and Expansion ROM

. The PCI Express Avalon-MM Bridge also translates the 32-bit

byte addresses used by the Application Layer to system-level physical addresses as

described in

“Avalon-MM-to-PCI Express Address Translation” on page 5–16

.

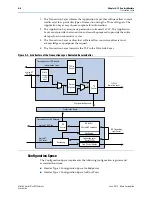

provides a high-level view of address translation in both directions.

Figure 5–7. Address Translation in TX and RX Directions

Transaction,

Data Link,

and PHY

DMA

Avalon-MM

32-Bit Byte Address

Avalon-MM

32-Bit Byte Address

PCIe TLP

Address

PCIe TLP

Address

Q

sys Gene

r

a

t

ed Endpoin

t

wi

t

h DMA Con

tr

olle

r

and On-Chip RAM

TX

PCIe

Link

RX

PCIe

Link

PCI Exp

r

ess Avalon-MM B

r

idge

Interconnect

Avalon-MM S

tr

a

t

ix V Ha

r

d IP fo

r

PCI Exp

r

ess

Number of address pages (1-512)

Size of address pages

Add

r

ess T

r

ansla

t

ion Table Pa

r

ame

t

e

r

s

Avalon-MM-

t

o-PCIe Add

r

ess T

r

ansla

t

ion

BAR (0-5)

BAR Type

BAR Size

PCI Base Add

r

ess Regis

t

e

r

s (BAR)

PCIe-

t

o-Avalon-MM Add

r

ess T

r

ansla

t

ion

On-

Chip

RAM

M

S

= RX Avalon-MM Master

= TX Avalon-MM Slave

S

M