Chapter 6: IP Core Interfaces

6–9

Avalon-ST RX Interface

June 2012

Altera Corporation

Stratix V Hard IP for PCI Express

1

The Avalon-ST protocol, as defined in

Avalon Interface Specifications

, is big endian,

while the Hard IP for PCI Express packs symbols into words in little endian format.

Consequently, you cannot use the standard data format adapters available in Qsys.

illustrates the mapping of Avalon-ST RX packets to PCI Express TLPs for a

three dword header with qword aligned addresses. Note that the byte enables

indicate the first byte of data is not valid and the last dword of data has a single valid

byte.

shows the mapping of Avalon-ST RX packets to PCI Express TLPs for TLPs

for a four dword header with qword aligned addresses with a 64-bit bus.

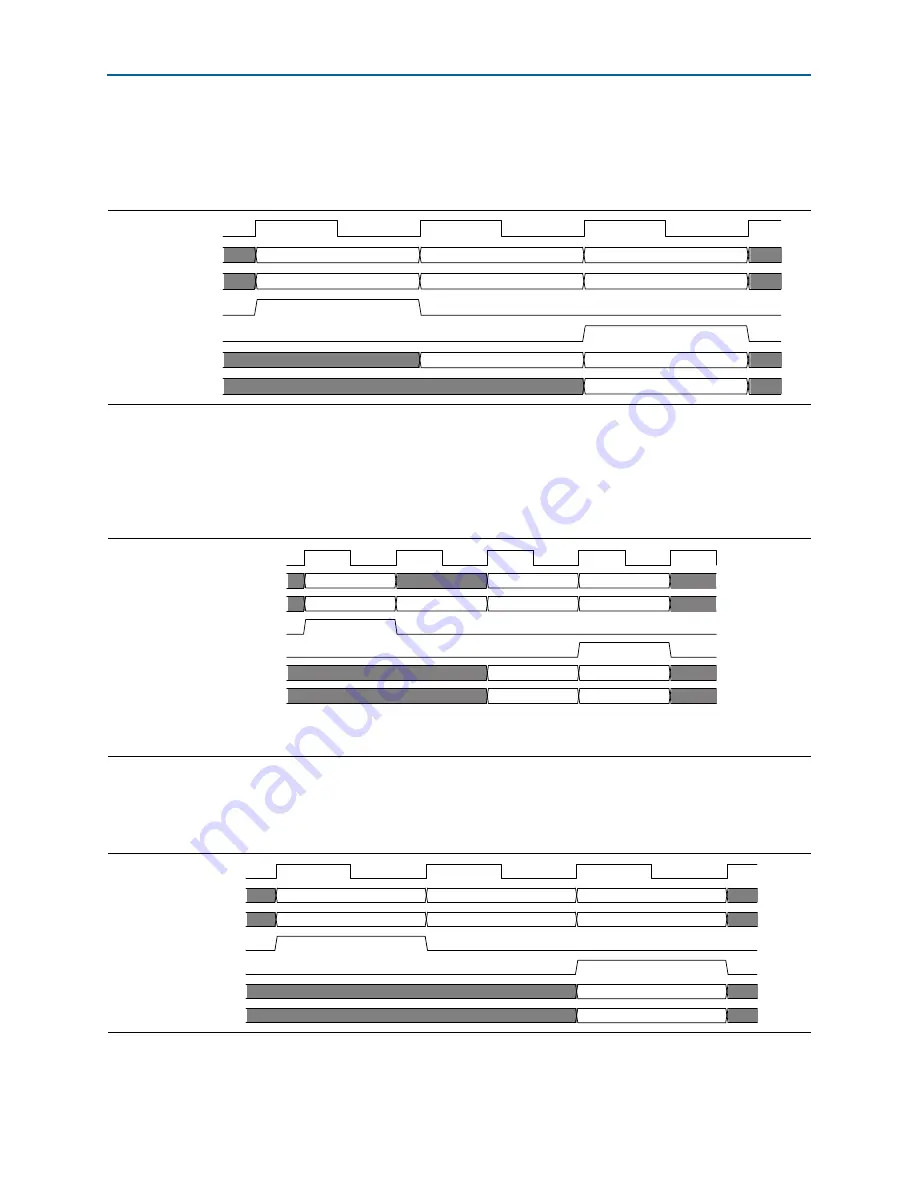

Figure 6–3. 64-Bit Avalon-ST rx_st_data

<n>

Cycle Definition for 3-Dword Header TLPs with Non-Qword Aligned Address

pld_clk

rx_st_data[63:32]

rx_st_data[31:0]

rx_st_sop

rx_st_eop

rx_st_be[7:4]

rx_st_be[3:0]

Header1

Data0

Data2

Header0

Header2

Data1

F

F

F

Figure 6–4. 64-Bit Avalon-ST rx_st_data<n> Cycle Definition for 3-Dword Header TLPs with Qword Aligned Address

Note to

(1)

rx_st_be[7:4]

corresponds to

rx_st_data[63:32]

.

rx_st_be[3:0]

corresponds to

rx_st_data[31:0]

clk

rx_st_data[63:32]

rx_st_data[31:0]

rx_st_sop

rx_st_eop

rx_st_be[7:4]

rx_st_be[3:0]

Header 1

Data1

Data3

Header 0

Header2

Data0

Data2

F

1

F

E

Figure 6–5. 64-Bit Avalon-ST rx_st_data

<n>

Cycle Definitions for 4-Dword Header TLPs with Qword Aligned Addresses

pld_clk

rx_st_data[63:32]

rx_st_data[31:0]

rx_st_sop

rx_st_eop

rx_st_be[7:4]

rx_st_be[3:0]

header1

header3

data1

header0

header2

data0

F

F