Chapter 6: IP Core Interfaces

6–63

Test Signals

June 2012

Altera Corporation

Stratix V Hard IP for PCI Express

describes the

test_in

bus signals. In Qsys these signals have the prefix,

hip_ctrl_

.

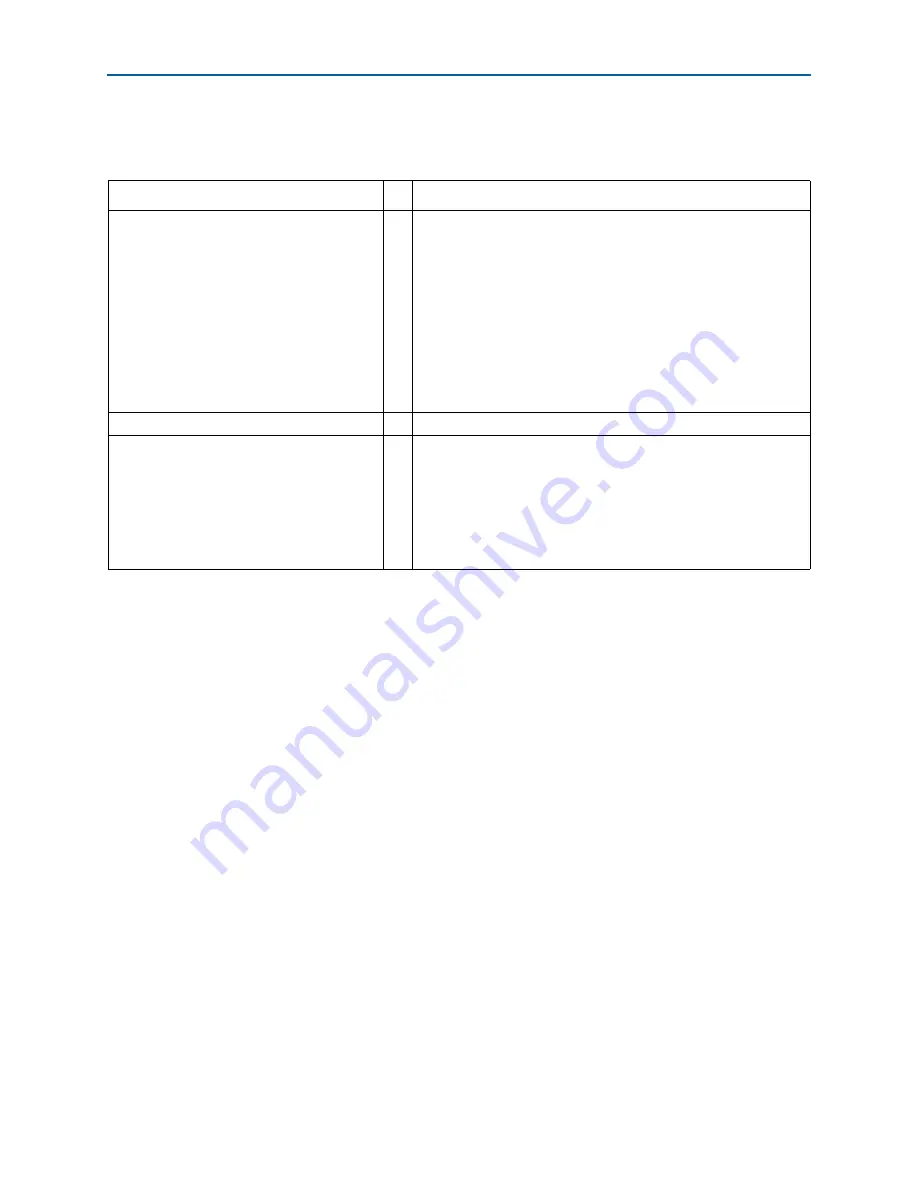

Table 6–32. Test Interface Signals

Signal

I/O

Description

test_in[31:1]

I

The bits of the

test_in

bus have the following definitions:

■

[0]: Simulation mode. This signal can be set to 1 to accelerate

initialization by reducing the value of many initialization counters.

■

[4:1]: Reserved. Must be set to 5’b01000.

■

[5]: Compliance test mode. Disable/force compliance mode. When

set, prevents the LTSSM from entering compliance mode.

Toggling this bit controls the entry and exit from the compliance

state, enabling the transmission of Gen1, Gen2 and Gen3

compliance patterns.

■

[31:6]–Reserved. Must be set to 26’h2.

simu_mode_pipe

O

When set to 1, the PIPE interface is in simulation mode.

lane_act[3:0]

Lane Active Mode: This signal indicates the number of lanes that

configured during link training. The following encodings are defined:

■

4’b0001: 1 lane

■

4’b0010: 2 lanes

■

4’b0100: 4 lanes

■

4’b1000: 8 lanes

Notes to

(1) All signals are per lane.

(2) Refer to

“PIPE Interface Signals” on page 6–60

for definitions of the PIPE interface signals.