ADSP-2126x SHARC Processor Hardware Reference

A-99

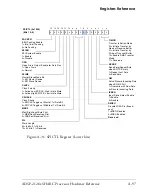

Registers Reference

11

CLKPL

Clock Polarity.

0 = Active-high SPICLK (SPICLK low is the idle state)

1 = Active-low SPICLK (SPICLK high is the idle state)

12

SPIMS

Master Select.

Configures SPI module as master or slave

0 = Device is a slave device

1 = Device is a master device

13

OPD

Open Drain Output Enable.

Enables open drain data output

enable (for MOSI and MISO)

0 = Normal

1 = Open Drain

14

SPIEN

SPI Port Enable.

0 = SPI Module is disabled

1 = SPI Module is enabled

15

PACKEN

Packing Enable.

0 = No Packing

1 = 8-16 Packing

Note: This bit may be 1 only when WL = 00 (8-bit transfer).

When in transmit mode, PACKEN bit will unpack data.

16

SGN

Sign Extend Bit.

0 = No sign extension

1 = Sign Extension

17

SMLS

Seamless Transfer Bit

.

0 = Seamless transfer disabled

1 = Seamless transfer enabled not supported in mode

TIMOD[1:0] = 00 and CPHASE = 0 for all modes.

18

TXFLSH

Flush Transmit Buffer.

Write a 1 to this bit to clear TXSPI

0 = TXSPI not Cleared

1 = TXSPI Cleared

19

RXFLSH

Clear RXSPI.

Write a 1 to this bit to clear RXSPI

0 = RXSPI not Cleared

1 = RXSPI Cleared

31–20

Reserved

Table A-27. SPICTL Register Bit Descriptions (Cont’d)

Bits

Name

Definition

Summary of Contents for ADSP-21261 SHARC

Page 30: ...Contents xxx ADSP 2126x SHARC Processor Hardware Reference ...

Page 40: ...Register Diagram Conventions xl ADSP 2126x SHARC Processor Hardware Reference ...

Page 58: ...Differences From Previous SHARCs 1 18 ADSP 2126x SHARC Processor Hardware Reference ...

Page 112: ...Secondary Processing Element PEy 2 54 ADSP 2126x SHARC Processor Hardware Reference ...

Page 178: ...Summary 3 66 ADSP 2126x SHARC Processor Hardware Reference ...

Page 204: ...DAG Instruction Summary 4 26 ADSP 2126x SHARC Processor Hardware Reference ...

Page 322: ...Setting Up DMA 7 32 ADSP 2126x SHARC Processor Hardware Reference ...

Page 436: ...SPORT Programming Examples 9 86 ADSP 2126x SHARC Processor Hardware Reference ...

Page 521: ...ADSP 2126x SHARC Processor Hardware Reference 11 31 Input Data Port rts IDP_ISR end ...

Page 522: ...Input Data Port Programming Example 11 32 ADSP 2126x SHARC Processor Hardware Reference ...

Page 590: ...Timer Programming Examples 14 20 ADSP 2126x SHARC Processor Hardware Reference ...

Page 796: ...I O Processor Registers A 174 ADSP 2126x SHARC Processor Hardware Reference ...

Page 800: ...B 4 ADSP 2126x SHARC Processor Core Manual ...

Page 846: ...Index I 36 ADSP 2126x SHARC Processor Hardware Reference ...