5 Implementation of EtherNet/IP

5.3 VSC-Vendor Specific Classes

XI/ON: XNE-GWBR-2ETH-IP

09/2011 MN05002007Z-EN

www.eaton.com

133

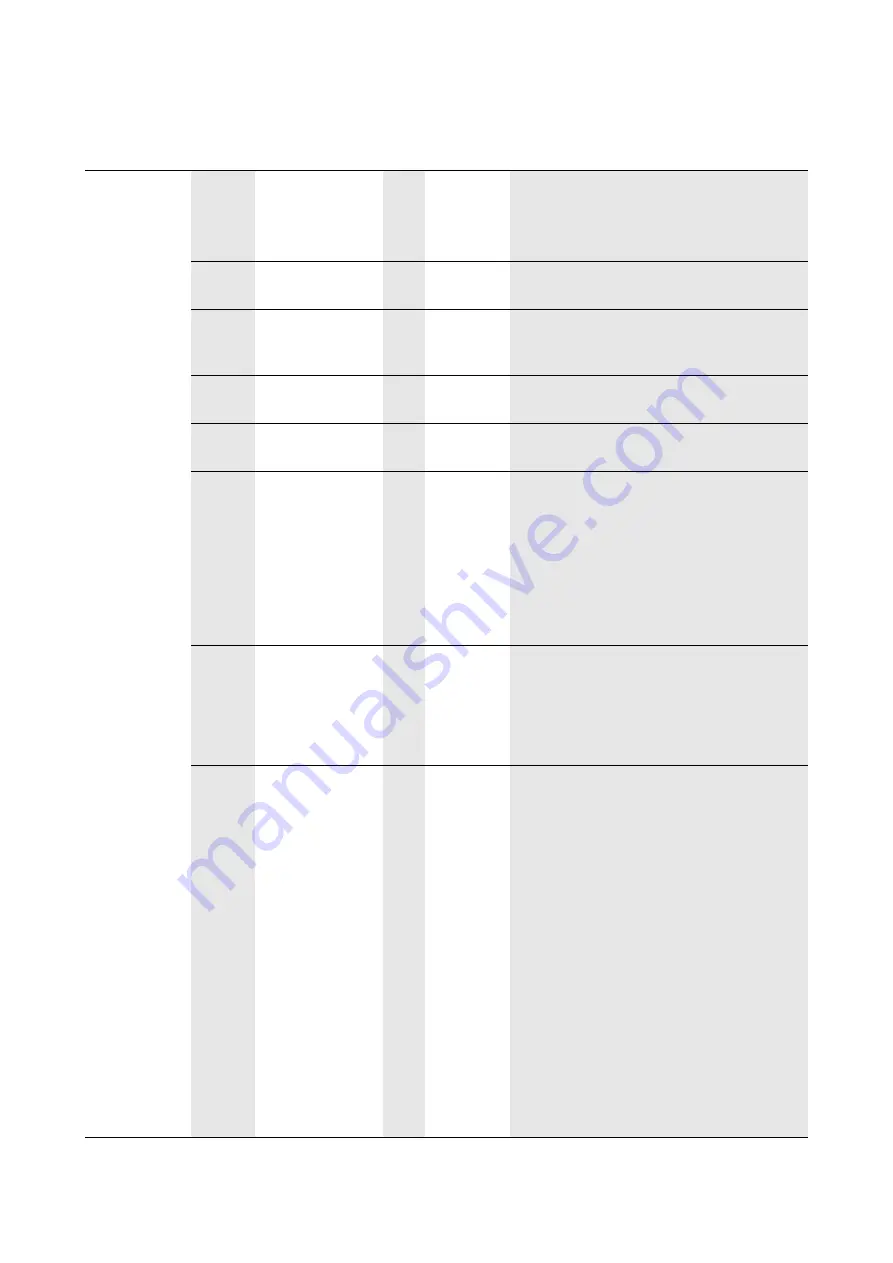

117

(75h)

Control

G/S WORD

Bit 13 to 15: reserved

118

(76h)

Address read

register

G/S

UINT

Address of the register with contents stated

in "Value read register" when "Result read

operation" 7 = 0.

119

(77h)

Address write

register

G/S

UINT

Address of the register to be written with

"Value write register".

120

(78h)

Value write

register

G/S

DWORD

Value to be written to the register with the

address stated at "Address write register".

121

(79h)

Write operation

G/S BOOL

0 = Default status, i.e. there is no request to

overwrite the content of the register

address stated at "Address write register"

with "Value write register". Bit 6 of the

"Result write operation" attribute is reset

(=0) if necessary.

1 = Request to overwrite the content of the

register at the address "Address write

register" with "Value write register".

122

(7Ah)

Write register and

execute

S STRUCTO

F UINT

DWORD

The structure contains both parts:

– Address of the register to be written.

– Value to be written.

The write operation is executed without

checking whether a write job is already

present.

123

(7Bh)

Diagnostics

G

WORD

Bit 0:

– 0 = No enabled status signal is active

(SSI_STSx = 0).

– 1 = "group diagnostics"

At least one enabled status signal is active

(SSI_STSx = 1).

Bit 1:

0 = SSI encoder signal present.

– 1 = "SSI error/open circuit" SSI encoder

signal faulty. (e.g. due to a cable break).

Bit 2:

– 0 = A comparison of the register contents

has produced the following result:

(REG_SSI_POS)

≦

(REG_UPPER_LIMIT)

– 1 = "error POS > UPPER LIMIT" A compar-

ison of the register contents has produced

the following result: (REG_SSI_POS) >

(REG_UPPER_LIMIT)

Table 58:

Object instance

Attr.

no.

dec.

(hex.)

Attribute name

G

et/

S

et

Type

Description