Operation

Fieldgate FXA42

52

Hauser

Unit

Description

State

Active

Sel

Next0

Cond0

State Machine 0

A0034300-EN

This unit represents the state of a state machine. There are eight different state machine units (

state

machine 0

to

state machine 7

), allowing you to implement eight independent state machines.

A state machine is implemented by placing various state machine units with the same state machine

index (e.g. state machine 0). The value of the input port

Sel

(32-bit signed integer) of the relevant unit

determines which state is handled by it. A state machine unit checks its Boolean input ports

Cond<X>

when it becomes active (state =

Sel

). If one of the Boolean input ports is set to

1

, the state machine

changes its state – which is determined by the corresponding input port

Next<X>

(32-bit signed

integer) – after the current IPO cycle.

The output port

State

(32-bit signed integer) displays the current state of the state machine. The

Boolean output port

Active

indicates that the corresponding unit is currently active (state of the state

machine =

Sel

).

The initial state is

0

.

Sub

A0034306

This unit performs a subtraction. It subtracts the values of its second input port and the subsequent

input ports from its first input port and writes the difference to its output port.

The subtraction is performed in the largest numeric data type of all the output ports that are

connected to the input ports of the unit. All the ports of the unit adopt this data type.

T

Clk

T-FF

Q

A0034307

This unit represents an T-Flipflop. The Boolean output port has the value

0

. If the Boolean input port

T

is set to

1

, the Boolean output port changes its state with each rising edge on the Boolean input port

Clk

. If the input port

T

is set to

0

, the output port retains its previous value.

Int

En

Timer

Clk

A0034308

This unit represents a timer. It outputs a periodic clock signal on the Boolean output port

Clk

. The

duration of the signal is specified by the value of the input port

Int

(interval, 32-bit unsigned integer)

and must be a multiple (at least twice) of the cycle time of the PLC. If the value of the input port

Int

is

less than the cycle time or not divisible by the cycle time, the value is rounded up internally to the

nearest multiple of the cycle time. The clock signal is only generated as long as the Boolean input port

En

is set to

1

.

IN

PT

TOF

Q

ET

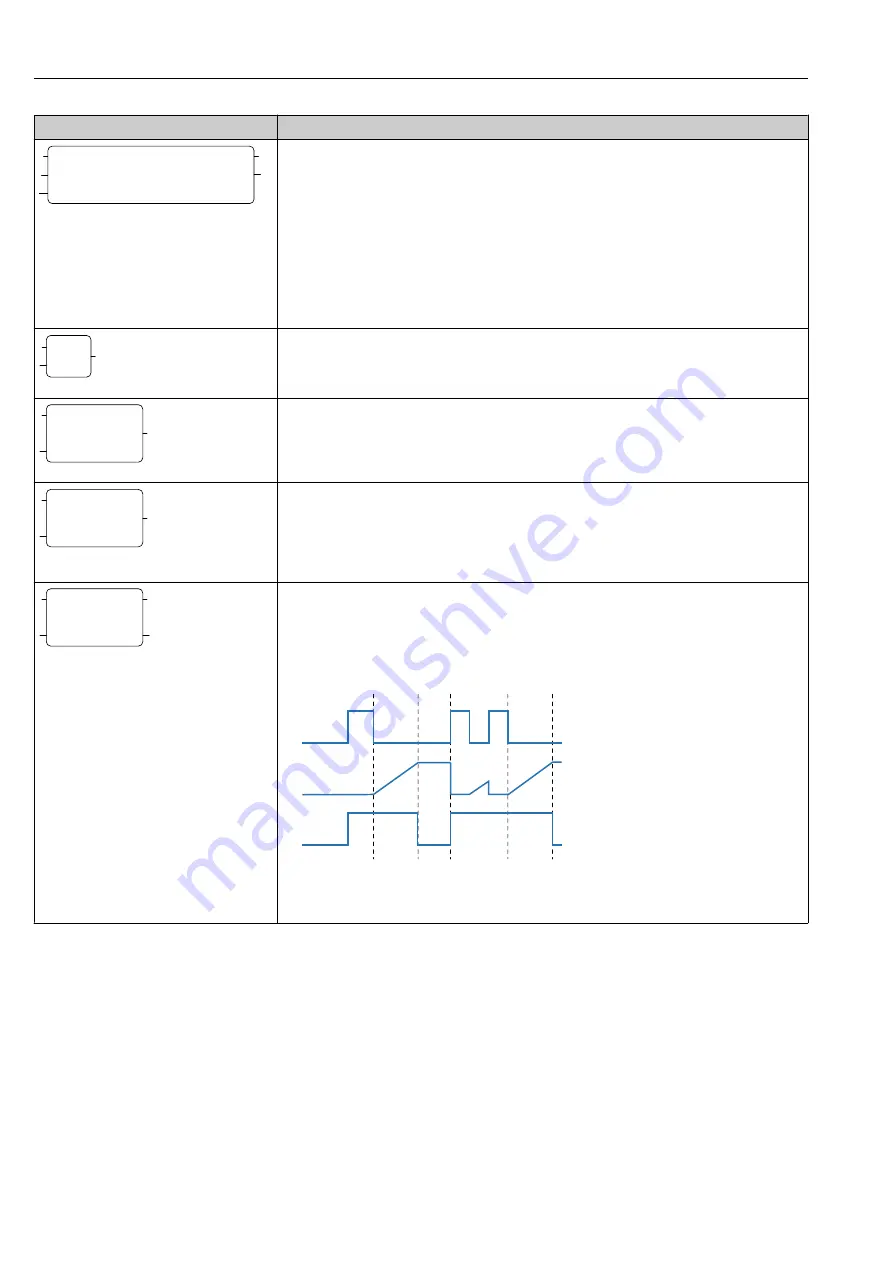

A0034309

This unit represents a timer off-delay.

When the Boolean input port

IN

switches to

1

, the Boolean output port

Q

is set to

1

. The timer is

started when the Boolean input port

IN

switches to

0

. The output port

ET

(elapsed time, 32-bit

unsigned integer) indicates how much time, in milliseconds, has elapsed since the timer was started.

When the value of the output port

ET

reaches the value of the input port

PT

(preset time, 32-bit

unsigned integer) the timer is stopped and the output port

Q

is reset.

IN

ET

Q

← →

PT

← →

PT

A0034332

If the value of the input port

Int

is less than the cycle time or not divisible by the cycle time, the

value is rounded up internally to the nearest multiple of the cycle time.