Rev. 1.50

1��

����st ��� �01�

Rev. 1.50

1�3

����st ��� �01�

HT66F0175/HT66F0185

A/D Flash MCU with EEPROM

HT66F0175/HT66F0185

A/D Flash MCU with EEPROM

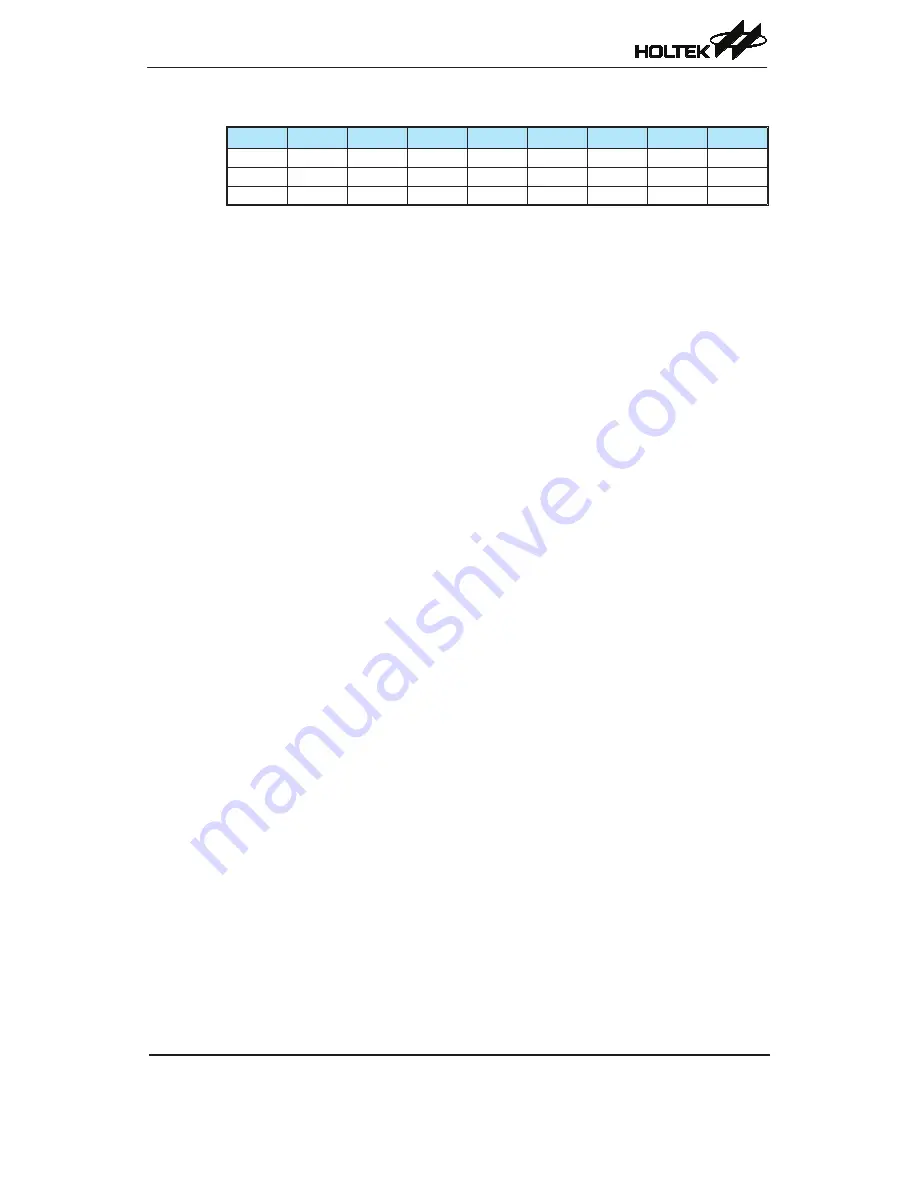

TBC Register

Bit

7

6

5

4

3

2

1

0

Name

TBON

TBCK

TB11

TB10

LXTLP

TB0�

TB01

TB00

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

POR

0

0

1

1

0

1

1

1

Bit 7

TBON

: Time Base function enable control

0: Disable

1: Enable

Bit 6

TBCK

: Time Base clock source select

0: f

TBC

1: f

SYS

/4

Bit 5~4

TB11~TB10

: Time Base 1 time-out period selection

00: 2

12

/f

TB

01: 2

13

/f

TB

10: 2

14

/f

TB

11: 2

15

/f

TB

Bit 3

LXTLP

: LXT Low Power control

0: Disable – LXT quick start-up

1: Enable – LXT slow start-up

Bit 2~0

TB02~TB00

: Time Base 0 time-out period selection

000: 2

8

/f

TB

001: 2

9

/f

TB

010: 2

10

/f

TB

011: 2

11

/f

TB

100: 2

12

/f

TB

101: 2

13

/f

TB

110: 2

14

/f

TB

111: 2

15

/f

TB

Serial Interface Module Interrupt

The Serial Interface Module Interrupt, also known as the SIM interrupt, is controlled by the SPI or

I

2

C data transfer. A SIM Interrupt request will take place when the SIM Interrupt request flag, SIMF,

is set, which occurs when a byte of data has been received or transmitted by the SIM interface,

an I

2

C slave address match or I

2

C bus time-out occurrence. To allow the program to branch to its

respective interrupt vector address, the global interrupt enable bit, EMI and the Serial Interface

Interrupt enable bit, SIME, must first be set. When the interrupt is enabled, the stack is not full and

any of the above described situations occurs, a subroutine call to the respective SIM Interrupt vector,

will take place. When the Serial Interface Interrupt is serviced, the EMI bit will be automatically

cleared to disable other interrupts. The SIMF flag will also be automatically cleared.

UART Transfer Interrupt – HT66F0185

The UART Transfer Interrupt is controlled by several UART transfer conditions. When one of these

conditions occurs, an interrupt pulse will be generated to get the attention of the microcontroller.

These conditions are a transmitter data register empty, transmitter idle, receiver data available,

receiver overrun, address detect and an RX pin wake-up. To allow the program to branch to its

respective interrupt vector address, the global interrupt enable bit, EMI, and UART Interrupt

enable bit, URE, must first be set. When the interrupt is enabled, the stack is not full and any of the

conditions described above occurs, a subroutine call to the UART Interrupt vector, will take place.

When the interrupt is serviced, the UART Interrupt flag, URF, will be automatically cleared. The

EMI bit will also be automatically cleared to disable other interrupts.