Copyright © Siemens AG 2010. All rights reserved.

Page

61

ERTEC 400 Manual

Technical data subject to change

Version 1.2.2

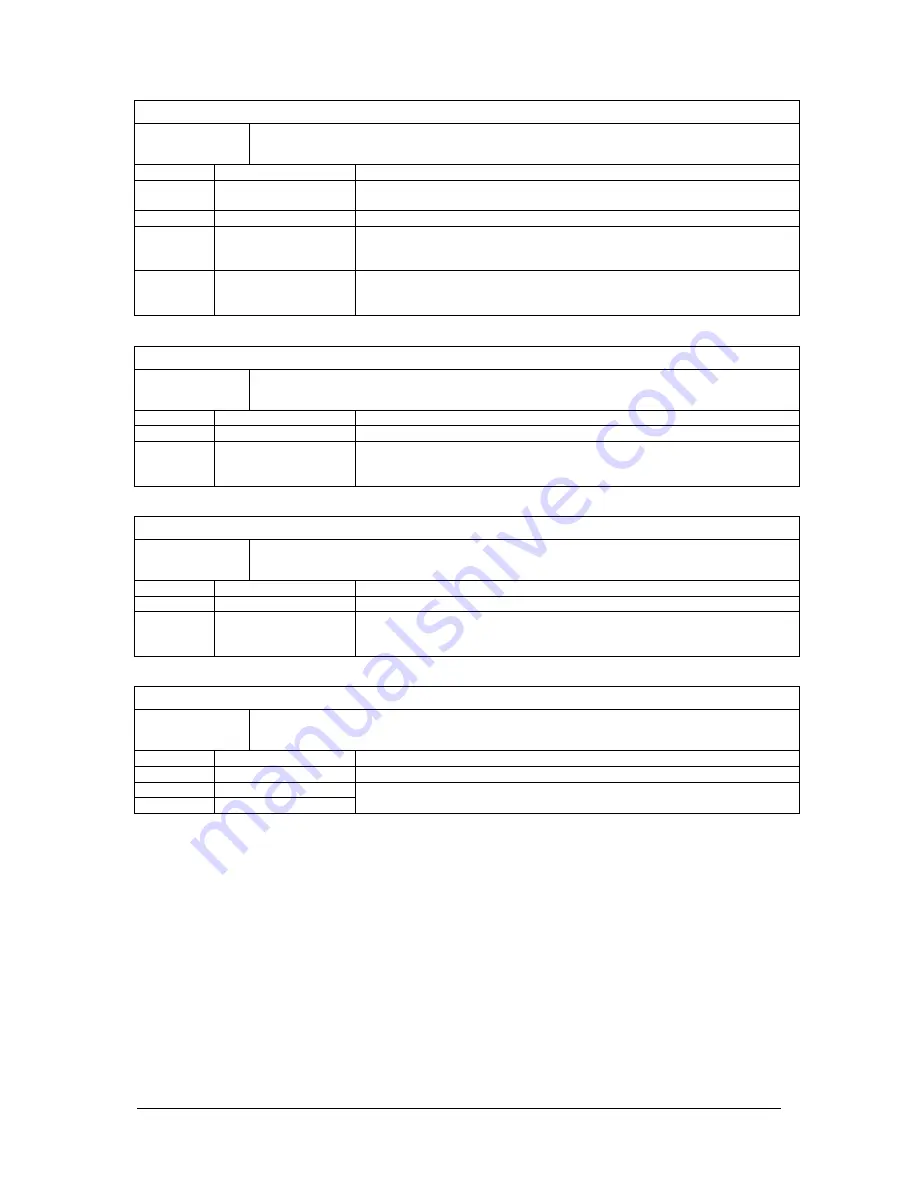

PCI_RES_REQ

R/W

Addr.: 0x4000_263C

Default: 0xFFFF_0002

Description

Request register for placing a soft reset request on the PCI bridge

Bit No.

Name

Description

31:16

MAX_DELAY_PCI

Number of AHB clock cycles allowed to elapse without a response on the

AHB-PCI bridge before a timeout is triggered.

15:2

----

Reserved

1

PCI_QVZ_EN

Enable of timeout monitoring of AHB accesses to the PCI bridge.

0: Monitoring inactive

1: Monitoring active

0

PCI_SOFT_RES_REQ

PCI bridge requirement for soft reset

0: Request is inactive

1: Request is active

PCI_RES_ACK

R

Addr.: 0x4000_2640

Default: 0x0000_0000

Description

Acknowledge register for display of an implemented soft reset request

Bit No.

Name

Description

31:1

----

Reserved

0

PCI_SOFT_RES_ACK

Display of implemented soft reset by PCI bridge

0: Request was not implemented

1: Request was implemented

MEM_SWAP

R/W

Addr.: 0x4000_2644

Default: 0x0000_0000

Description

Memory swapping in Segment 0 between ROM and RAM

Bit No.

Name

Description

31:1

----

Reserved

0

MEM_SWAP

Selection of memory in Segment 0:

0: Boot ROM starting with Addr 0h

1: Internal user RAM starting with Adr 0h

PCI_INT_CTRL

R/W

Addr.: 0x4000_2648

Default: 0x0000_0000

Description

Control of PCI interrupts

Bit No.

Name

Description

31:2

----

Reserved

1

PCI_INT_CTRL[1]

0

PCI_INT_CTRL[0]

PCI_INT_CTRL = 0x0000_0001 IRQ0_HP

SERR_N

PCI_INT_CTRL = 0x0000_0000 IRQ0_HP

INTB_N