SERIES IP1K110 INDUSTRIAL I/O PACK RECONFIGURABLE DIGITAL I/O MODULE

__________________________________________________________________________________________

- 11 -

Acromag, Inc. Tel:248-295-0310 Fax:248-624-9234 Email:solutions@acromag.com

http://www.acromag.com

The address specified in the Memory Address register will be

automatically incremented after the read or write cycle is

completed. Thus, when consecutive locations within the memory

are accessed the Memory Address register need not be manually

updated by software.

Read or write accesses to this register require four wait

states. A software or hardware reset has no affect on this

register.

Memory Address Register (Write Only, 16H)

The Memory Address register is used to point to one of 64K

words in memory. The 16 bits of this register are used to specify

one of 64K words that can be accessed via a read or write to the

Memory Data register. Writing to this register is possible via 16-

bit data transfers only.

The address specified in the Memory Address register will be

automatically incremented after the read or write cycle to the

Memory Data register is completed. Thus, when consecutive

locations within the memory are accessed the Memory Address

register need not be manually incremented by software.

A write access to this register requires one wait state. A

software or hardware reset will clear this register to zero.

Clock Control Reg 1 (Read/Write) – (Base + 18H)

The Clock Control Register 1 is a 16-bit read/write register.

This is used as part of the control for the Cypress CY22150

Programmable Clock. The register contains the following control

bits as specified in the Cypress CY22150 spec sheet.

Bit

Data

Bit

Data

D0

DIV1N(0)

D8

Q(0)

D1

DIV1N(1)

D9

Q(1)

D2

DIV1N(2)

D10

Q(2)

D3

DIV1N(3)

D11

Q(3)

D4

DIV1N(4)

D12

Q(4)

D5

DIV1N(5)

D13

Q(5)

D6

DIV1N(6)

D14

Q(6)

D7

DIV1SRC

D15

PO

A software or hardware reset will clear this register to zero.

Clock Control Reg 2 (Read/Write) – (Base + 1AH)

The Clock Control Register 2 is a 16-bit read/write register.

This is used as part of the control for the Cypress CY22150

Programmable Clock. The register contains the following control

bits as specified in the Cypress CY22150 spec sheet.

Bit

Data

Bit

Data

D0

PB(0)

D8

PB(8)

D1

PB(1)

D9

PB(9)

D2

PB(2)

D10

Pump(0)

D3

PB(3)

D11

Pump(1)

D4

PB(4)

D12

Pump(2)

D5

PB(5)

D13

CLKSRC0

D6

PB(6)

D14

CLKSRC1

D7

PB(7)

D15

CLKSRC2

A software or hardware reset will clear this register to zero.

Clock Control Reg 3 (Read/Write) – (Base + 1DH)

The Clock Control Register 3 is an 8-bit read/write register.

This is used as part of the control for the Cypress CY22150

Programmable Clock. In this register only D0 (bit 0) and D7 (bit

7) are required. The other bits (D1-D6) are not used.

The value for D0 is zero if the carrier board provides an 8MHz

clock to the FPGA. D0 is logic high if the carrier board provides a

32MHz signal to the FPGA. D7 is an enable/disable signal for the

CY22150 IC. Writing a ‘1’ to bit 7 will disable the clock generator

chip, including the programming function. Setting D7 to zero will

allow for normal operation. A software or hardware reset will

clear this register to zero.

Clock Trigger Register (Read/Write) – (Base + 1FH)

The Clock Trigger Register is an 8-bit register. To initiate

programming of the Cypress CY22150 Programmable Clock,

write a “1” to bit 0 of this register. During programming bit 0 will

remain logic high. The programming process takes

approximately 1.2ms to complete after the initial trigger. A

software or hardware reset has no affect on this register.

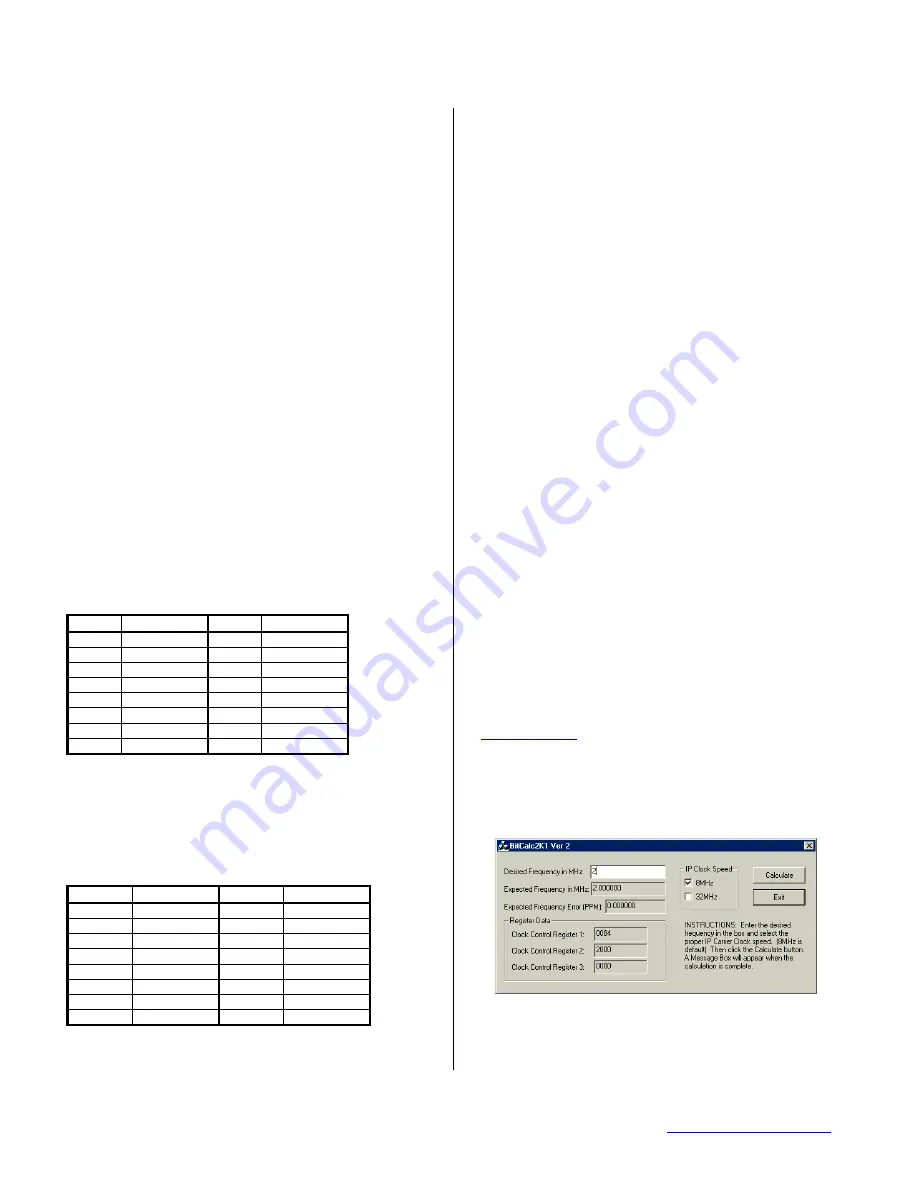

Program Procedure to Set Clock Frequency

At power up the programmable clock has no valid output.

The clock can be programmed for an output frequency from

250 KHz to 100 MHz. The clock can be programmed at any time

during device operation. Program the clock using the following

process.

The program words required for Clock Control Register 1, 2,

and 3 can be calculated using a program provided by Acromag

(BitCalc2K1 Version 2) supplied with the EDK. Alternately, using

the Clock Control Registers Data Maps and the CY22150

specification sheet the necessary values can be calculated.

Cypress has a program CyberClocks available to aid with

calculations. Note that the user will have to combine the

individual variables into the control words as outlined in the

register descriptions. The CY22150 Specification Sheets and

CyberClocks program are available from Cypress

at

www.cypress.com

.

The reference frequency input to the Cypress CY22150 is the

same as the carrier clock either 8MHz or 32MHz.

Procedure

1.

Start the BitCalc2K1 Version 2 program, enter the desired

frequency, and select the IP clock speed.

2.

Hit the Calculate Button.

3.

Write to the Clock Control Register 1 at base address plus

an offset of 18H using the data provided by the program.

4.

Write to the Clock Control Register 2 at base address plus

an offset of 1AH using the data provided by the program.