SERIES IP1K110 INDUSTRIAL I/O PACK RECONFIGURABLE DIGITAL I/O MODULE

__________________________________________________________________________________________

- 8 -

Acromag, Inc. Tel:248-295-0310 Fax:248-624-9234 Email:solutions@acromag.com

http://www.acromag.com

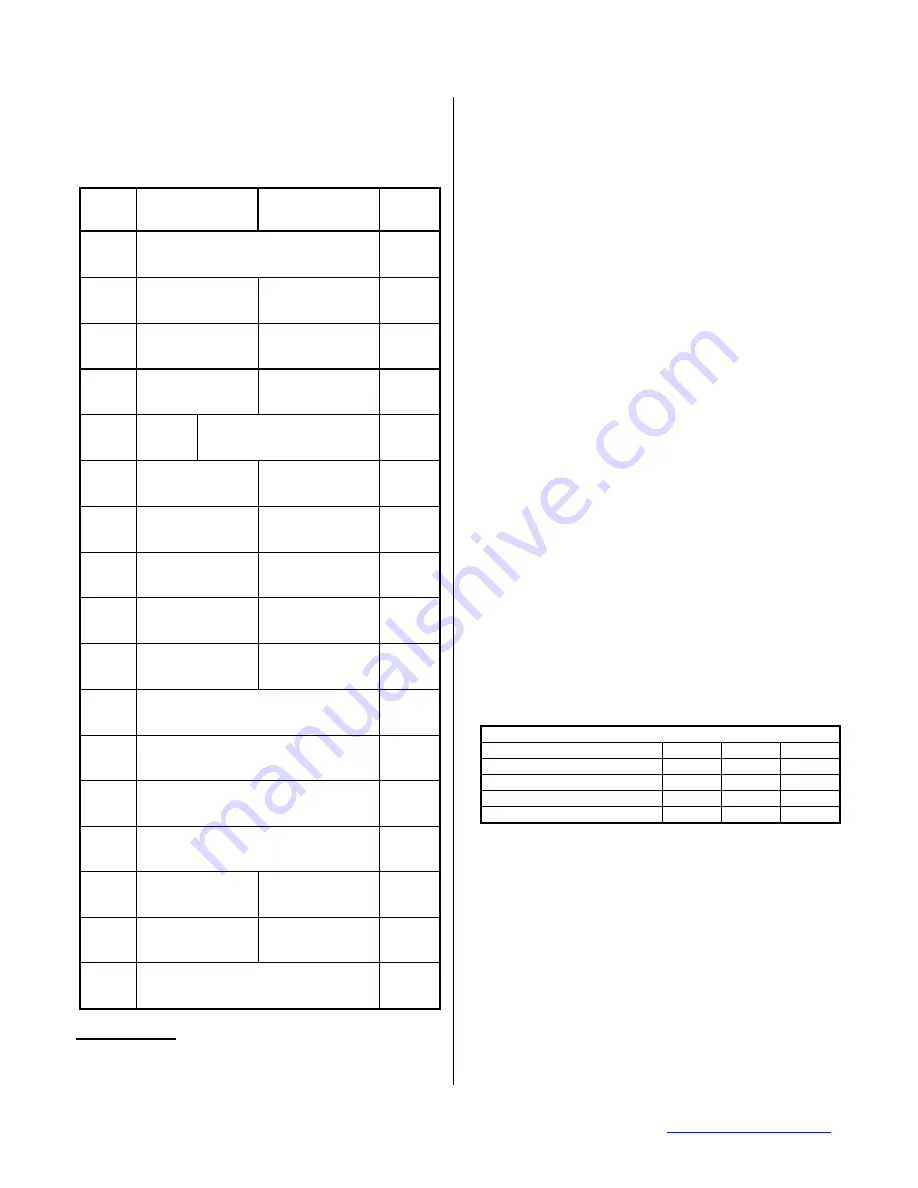

The I/O space address map for this example design is given

in Table 3.3. The differential or TTL I/O, clock generator chip,

and 64K x 16 static RAM can be controlled and accessed through

I/O space.

Table 3.3: IP1K110 FPGA Address Map (IO Space)

EVEN

Base

Addr.+

EVEN Byte

D15 D08

ODD Byte

D07 D00

ODD

Base

Addr.+

00

Control Register

01

02

Input/Output

Registers

CH15

↔

CH08

Input/Output

Registers

CH07

↔

CH00

03

04

Input/Output

Registers

CH31

↔

CH24

Input/Output

Registers

CH23

↔

CH16

05

06

Input/Output

Registers

CH47

↔

CH40

Input/Output

Registers

CH39

↔

CH32

07

08

Not

Used

1

Direction Control

Register

Bit11

↔

Bit0

09

0A

Not Used

1

R/W - Interrupt

Enable Channels

CH07

↔

CH00

0B

0C

Not Used

1

R/W - Interrupt

Type Channels

CH07

↔

CH00

0D

0E

Not Used

1

R/W - Interrupt

Status Channels

CH07

↔

CH00

0F

10

Not Used

1

R/W - Interrupt

Polarity Channels

CH07

↔

CH00

11

12

Not Used

1

Interrupt Vector

Register

13

14

Memory Data Register

15

16

Memory Address Register

17

18

Clock Control Register 1

19

1A

Clock Control Register 2

1B

1C

NOT USED

1

Clock Control

Register 3

1D

1E

NOT USED

1

Clock Generator

Trigger Register

1F

20

↓

↓

↓

↓

7E

NOT USED

1

21

↓

↓

↓

↓

7F

Notes (Table 3.3):

1. The IP will respond to addresses that are "Not Used" with an

active IP module acknowledge ACK

∗

. Data read at “Not

Used” addresses will be driven low.

The base address for the IP module I/O space (see your

carrier board instructions) must be added to the addresses shown

in Table 3.3 to properly access the I/O space. Accesses can be

performed on an 8-bit (D08[EO]), or 16-bit (D16) word basis.

The memory map for this module is given assuming byte

accesses using the “Big Endian” byte ordering format. Big

Endian is the convention used in the Motorola 68000 and

PowerPC microprocessor family and is the VMEbus convention.

In Big Endian, the lower-order byte is stored at odd-byte

addresses. The Intel x86 family of microprocessors uses the

opposite convention, or “Little Endian” byte ordering. Little

Endian uses even-byte addresses to store the low-order byte. As

such, use of the memory map for this module on a PC carrier

board will require the use of the even address locations to access

the lower 8-bit data. On a VMEbus carrier use of odd address

locations are required to access the lower 8-bit data as shown in

Table 3.1 and 3.3.

Control Register (Read/Write) - (Base + 00H)

This read/write register is used to transfer control back to

configuration mode when in user mode, set your specific model

of the IP1K110, and issue a software reset.

Bit-0 controls operation of the IP1K110 in user mode and

configuration mode via control of pin 168 of the Altera FPGA.

When bit-0 is set to logic low the IP1K110 will be in user mode.

Setting bit-0 to a logic high places the IP1K110 in configuration

mode. Upon issue of an IP bus reset, this register bit will be clear

placing the IP1K110 in user mode. Also, initial configuration of

the Altera FPGA sets bit-0 to a logic low holding the FPGA in

user mode.

Bits 10 to 8 are used to set the IP1K110 model

corresponding to your I/O mix. This will allow the Altera FPGA to

properly map Input/Output registers to the I/O transceivers

present on your module. Bits 10 to 8 should be set as identified

in the following table to identify the model corresponding to your

IP1K110.

Control Register Bits 10, 9, and 8

IP Model

Bit-10

Bit-9

Bit-8

Disabled

0

0

0

IP1K110-0024

0

0

1

IP1K110-2412

1

0

0

IP1K110-4800

1

1

1

Bit-11 is reserved for factory testing. (See EDK

documentation for further details.) For normal operation this bit

should be set to logic low.

Bit-15 can be used to issue a software reset. When bit-15 is

set to a logic high a software reset will occur.

Reading this register will return logic low on all data lines/bits

except for bits 11 to 8 and bit-0 which will reflect their last written

state.