SERIES IP1K110 INDUSTRIAL I/O PACK RECONFIGURABLE DIGITAL I/O MODULE

_________________________________________________________________________________________

- 2 -

Acromag, Inc. Tel:248-295-0310 Fax:248-624-9234 Email:solutions@acromag.com

http://www.acromag.com

The information contained in this manual is subject to change

without notice. Acromag, Inc. makes no warranty of any kind with

regard to this material, including, but not limited to, the implied

warranties of merchantability and fitness for a particular purpose.

Further, Acromag, Inc. assumes no responsibility for any errors

that may appear in this manual and makes no commitment to

update, or keep current, the information contained in this manual.

No part of this manual may be copied or reproduced in any form,

without the prior written consent of Acromag, Inc.

Table of Contents

Page

1.0 GENERAL INFORMATION

….......................................

2

KEY IP1K110 FEATURES............................................

3

INDUSTRIAL I/O PACK INTERFACE FEATURES........

3

SIGNAL INTERFACE PRODUCTS...............................

3

IP MODULE Win32 DRIVER SOFTWARE……………..

4

IP MODULE VxWORKS SOFTWARE...........................

4

2.0 PREPARATION FOR USE

............................................

4

UNPACKING AND INSPECTION..................................

4

CARD CAGE CONSIDERATIONS................................

4

BOARD CONFIGURATION...........................................

4

CONNECTORS.............................................................

4

IP Field I/O Connector (P2).......................................

4

I/O Noise and Grounding Considerations..................

5

IP Logic Interface Connector (P1)..............................

5

3.0

PROGRAMMING INFORMATION

.................................

6

IN-SYSTEM CONFIGURATION ADDRESS MAPS.......

6

IP1K110 Configuration Procedure.............................

6

Altera FPGA Logic Requirements..............................

6

IP Identification Space...............................................

7

Example Altera FPGA Design...................................

7

Control Register........................................................

8

Input/Output Registers...............................................

9

Direction Control Register..........................................

9

Interrupt Enable Register...........................................

9

Interrupt Type Configuration Register........................

9

Interrupt Status Register............................................

10

Interrupt Polarity Register..........................................

10

Interrupt Vector Register...........................................

10

Memory Data Register...............................................

10

Memory Address Register.........................................

11

Clock Control Register 1 ...........................................

11

Clock Control Register 2 ...........................................

11

Clock Control Register 3 ...........................................

11

Clock Trigger Register...............................................

11

Program Procedure to Set Clock Frequency.............

11

IP1K110 PROGRAMMING CONSIDERATIONS...........

12

Programming Interrupts.............................................

12

4.0

THEORY OF OPERATION

...........................................

13

FIELD INPUT/OUTPUT SIGNALS.................................

13

LOGIC/POWER INTERFACE.......................................

13

EIA-RS485 AND RS422 SERIAL INTERFACE..............

14

SIGNAL PIN ASSIGNMENTS.......................................

14

5.0

SERVICE AND REPAIR

................................................

16

SERVICE AND REPAIR ASSISTANCE........................

16

PRELIMINARY SERVICE PROCEDURE......................

16

6.0

SPECIFICATIONS

........................................................

16

PHYSICAL....................................................................

16

ENVIRONMENTAL........................................................

17

EIA-RS485/RS422 TRANSCEIVERS............................

17

TTL TRANSCEIVERS...................................................

17

INDUSTRIAL I/O PACK COMPLIANCE........................

IP1K110 ENGINEERING DESIGN KIT..........................

17

18

APPENDIX

...................................................................

18

CABLE: MODEL 5025-551............................................

18

CABLE: MODEL 5025-552............................................

18

TRANSITION MODULE: MODEL TRANS-GP...............

19

DRAWINGS

Page

4501-971 IP1K110 BLOCK DIAGRAM.........................

20

4501-702 RS485 I/O CONNECTIONS..........................

21

4501-434 IP MECHANICAL ASSEMBLY..................…

22

4501-462 CABLE 5025-550 (NON-SHIELDED)............

23

4501-463 CABLE 5025-551 (SHIELDED).....................

24

4501-464 TERMINATION PANEL 5025-552................

25

4501-465 TRANSITION MODULE TRANS-GP............

25

IMPORTANT SAFETY CONSIDERATIONS

It is very important for the user to consider the possible adverse

effects of power, wiring, component, sensor, or software failures

in designing any type of control or monitoring system. This is

especially important where economic property loss or human life

is involved. It is important that the user employ satisfactory

overall system design. It is agreed between the Buyer and

Acromag, that this is the Buyer's responsibility.

All trademarks are the property of their respective owners.

1.0 GENERAL INFORMATION

The Industrial I/O Pack (IP) Series IP1K110 module is a

reconfigurable digital input/output board. The IP1K110 contains a

100,000 gate Altera

Field Programmable Gate Array (FPGA)

which is in-system reconfigurable. This allows designers to

implement logic functions unique to their application and in-

system configure the Altera FPGA via the IP bus interface.

An example Altera FPGA configuration file and its

corresponding VHDL source are provided with the IP1K110

Engineering Design Kit. To take advantage of the example VHDL

program, the user must be proficient in the use of VHDL and the

Altera Maxplus II or Quartus II software tools.

The IP1K110 provides several different interface options

which allow a mix of differential digital and TTL digital input/output

channels. The models and their corresponding combination of

channels are given in the table below.

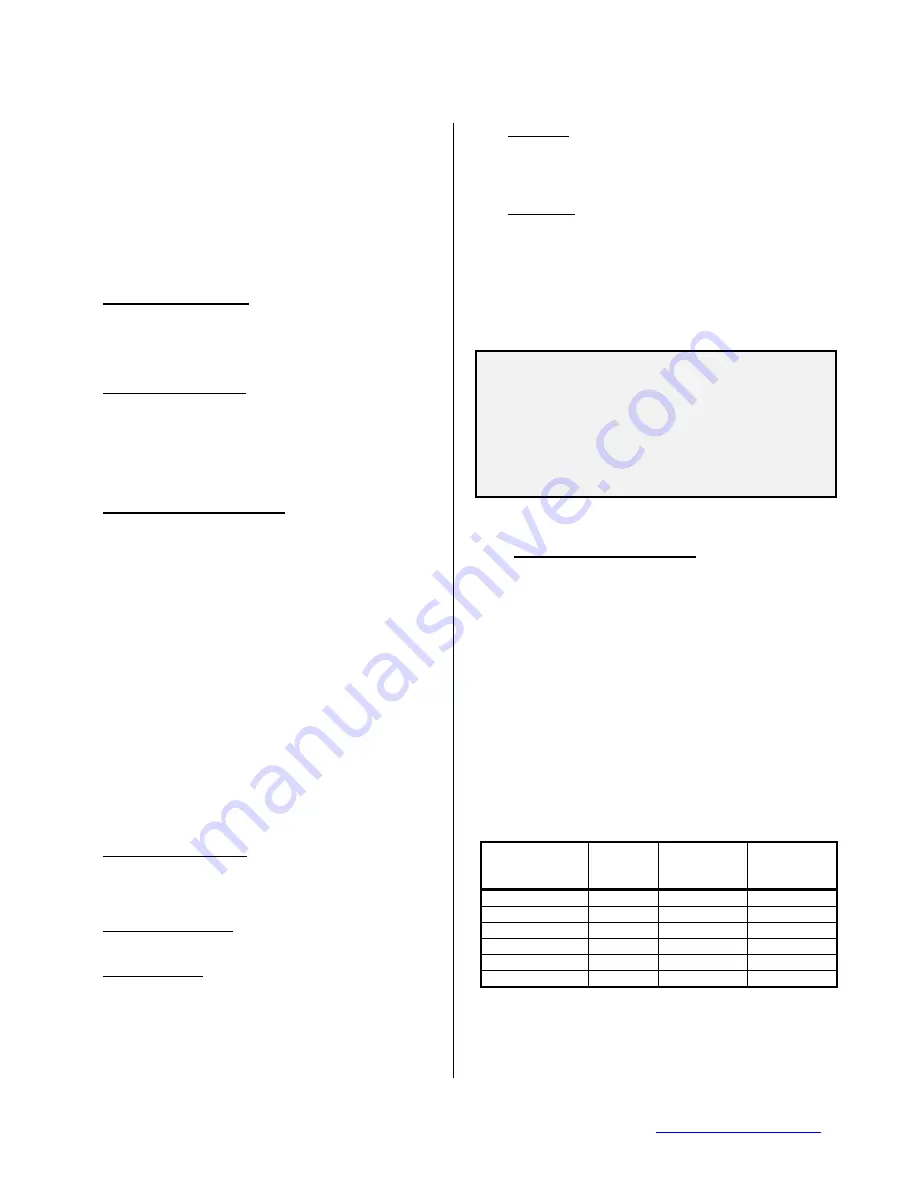

Model

TTL

Channels

EIA-485/422

Channels

Operating

Temperature

Range

IP1K110-0024

0

24

0 to 70°C

IP1K110-2412

24

12

0 to 70°C

IP1K110-4800

48

0

0 to 70°C

IP1K110-0024E

0

24

-40 to 85°C

IP1K110-2412E

24

12

-40 to 85°C

IP1K110-4800E

48

0

-40 to 85°C

The IP1K110 can be programmed to support all types of IP

cycles at either 8 or 32 MHz operation. The IP1K110 comes with

a simple example Altera design file that can be enhanced for

implementation of custom digital logic functions.