SERIES IP1K110 INDUSTRIAL I/O PACK RECONFIGURABLE DIGITAL I/O MODULE

__________________________________________________________________________________________

- 9 -

Acromag, Inc. Tel:248-295-0310 Fax:248-624-9234 Email:solutions@acromag.com

http://www.acromag.com

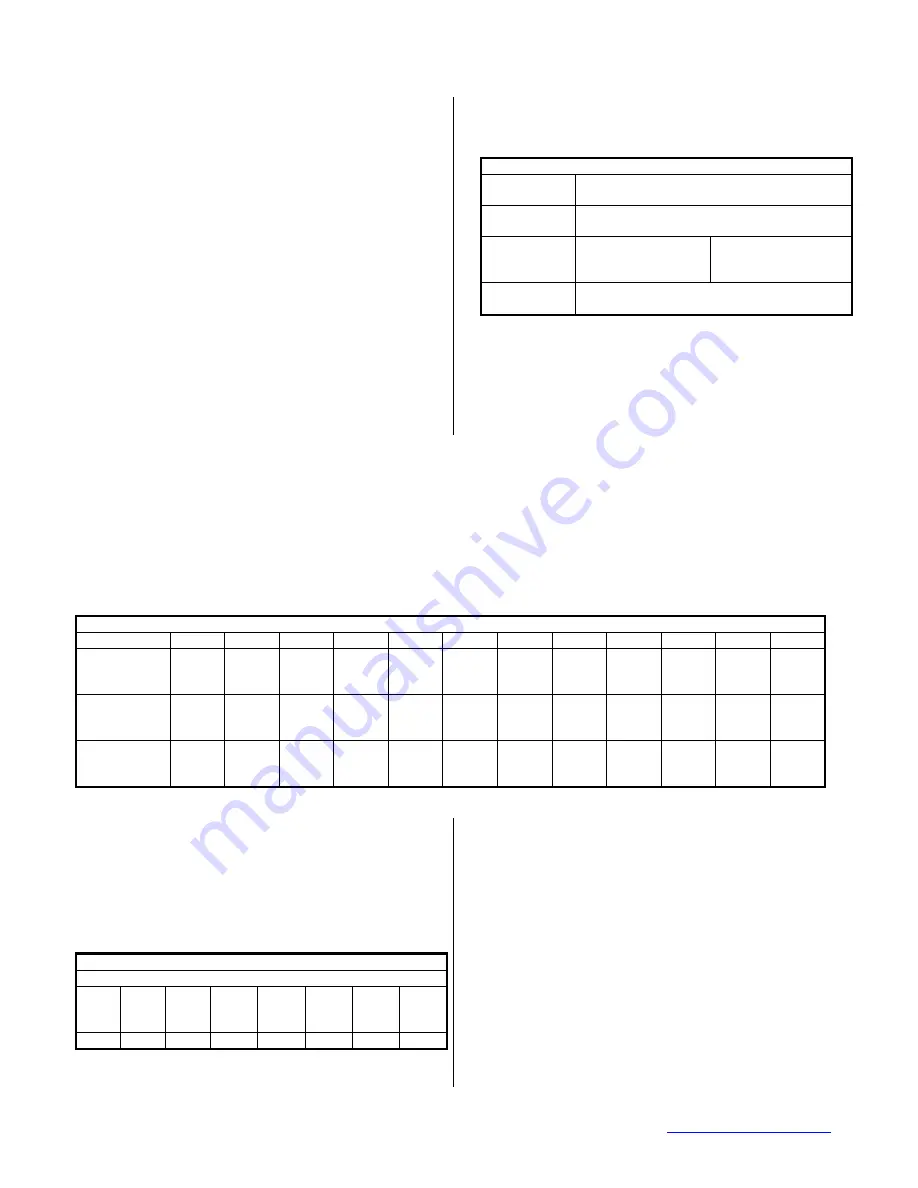

Input/Output Registers

(Read/Write) - (Base + 02H to 07H)

Forty-eight possible input/output channels numbered 0

through 47 may be individually accessed via these registers. The

Input/Output Channel registers are used to monitor/read or

set/write channels 0 through 47. The first eight channels are

accessed at the carrier base a03H via the low data byte.

The next eight channels are accessed at the carrier base address

+02H via the high data byte. The remaining 32 channels are

accessed similarly at the carrier base a offsets shown in

Table 3.3.

If the Input/Output port is to be selected as an output, you

should first set the output register bit as desired before setting the

Direction Control register. Note; if you select as output before

setting this Input/Output register, the output will be logic low as

this is the power-up/reset state of the output register bits.

Table 3.4 shows all channels and their corresponding I/O

data register bit for each of the IP1K110 models.

The register bits not listed will not be used. See the memory

map to identify the addresses required to control I/O registers.

Table 3.4: Input/Output Registers

Used Input/Output Channel Register Bits

Model

I/O Register Bits

See Table 2.1 for Pin Assignments

IP1K110-0024

Differential/RS485 Channels

±

0 to

±

23

Register Bits 0 to 23

IP1K110-2412

Differential /RS485

Channels

±

12 to

±

23

Register Bits 32 to 43

TTL Channels

0 to 23

Register Bits 0 to 23

IP1K110-4800

TTL Channels 0 to 47

Register Bits 0 to 47

Channel read/write operations use 8-bit, or 16-bit data

transfers with the lower ordered bits corresponding to the lower-

numbered channels for the register of interest. All input/output

channels are configured as inputs on a power-on or software

reset. The unused upper bits of these registers will always read

low (0’s).

Direction Control Register (Read/Write) - (Base + 08H and 09H)

The data direction (input or output), of the digital I/O channels, is selected via this register. The data direction of all differential channels

are set as a group of two or four channels while data direction of all TTL channels is controlled as a group of 8 channels. Setting a bit high

configures the data direction, for the identified channels, as output. Setting the control bit low configures the corresponding channel’s data

direction for input.

The default power-up state of these registers is logic low. Thus, all channels are configured as inputs on system reset or power-up. The

unused upper nibble (D15 to D12) of the register at base a 08H will always read low (0’s). All not used bits will also read low. See

Table 2.1 for field I/O pin assignments corresponding to each of the RS485 and TTL channels listed below.

Direction Control Register

Model

D11

D10

D09

D08

D07

D06

D05

D04

D03

D02

D01

D00

IP1K110-0024

Not

Used

Not

Used

Not

Used

Not

Used

Not

Used

Not

Used

Ch 10,

11, 22,

23

Ch

8,9,

20, 21

Ch 6,

7

18, 19

Ch

4,5,

16, 17

Ch

2,3,

14,15

Ch

0,1,

12, 13

IP1K110-2412

Not

Used

Not

Used

Not

Used

TTL

Ch 16-

Ch 23

TTL

Ch 8-

Ch 15

TTL

Ch 0-

Ch 7

Ch 22

Ch 23

Ch 20

Ch 21

Ch 18

Ch 19

Ch 16

Ch 17

Ch 14

Ch 15

Ch 12

Ch 13

IP1K110-4800

TTL

Ch 40-

Ch 47

TTL

Ch 32-

Ch 39

TTL

Ch 24-

Ch 31

TTL

Ch 16-

Ch 23

TTL

Ch 8-

Ch 15

TTL

Ch 0-

Ch 7

Not

Used

Not

Used

Not

Used

Not

Used

Not

Used

Not

Used

Interrupt Enable Registers (Read/Write) - (Base + 0BH)

The Interrupt Enable Registers provide a mask bit for the first

8 channels. A “0” bit will prevent the corresponding input channel

from generating an external interrupt. A “1” bit will allow the

corresponding input channel to generate an interrupt. Only those

channels enabled for interrupts can generate interrupts.

Interrupts are only available on the first eight channels.

Interrupt Enable Register

MSB

LSB

Data

Bit

07

Data

Bit

06

Data

Bit

05

Data

Bit

04

Data

Bit

03

Data

Bit

02

Data

Bit

01

Data

Bit

00

Ch07

Ch06

Ch05

Ch04

Ch03

Ch02

Ch01

Ch00

The Interrupt Enable register at the carrier’s base a

offset 0BH is used to control channels 00 through 07. For

example, channel 00 is controlled via data bit-0 as seen in the

prior table.

Channel read operations use 8-bit, or 16-bit data transfers.

The upper 8 bits of this register are “Not Used” and will always

read low (0’s) for D16 accesses.

All input channel interrupts are disabled (set to “0”) following

a power-on or software reset.

Interrupt Type (COS or H/L) Configuration Registers

(Read/Write) - (Base + 0DH)

The Interrupt Type Configuration Registers determine the

type of input channel transition that will generate an interrupt for

each of the 8 possible interrupting channels. A “0” bit selects