SERIES IP503 INDUSTRIAL I/O PACK EIA/TIA-232E & CENTRONICS COMMUNICATION MODULE

___________________________________________________________________________________________

- 12 -

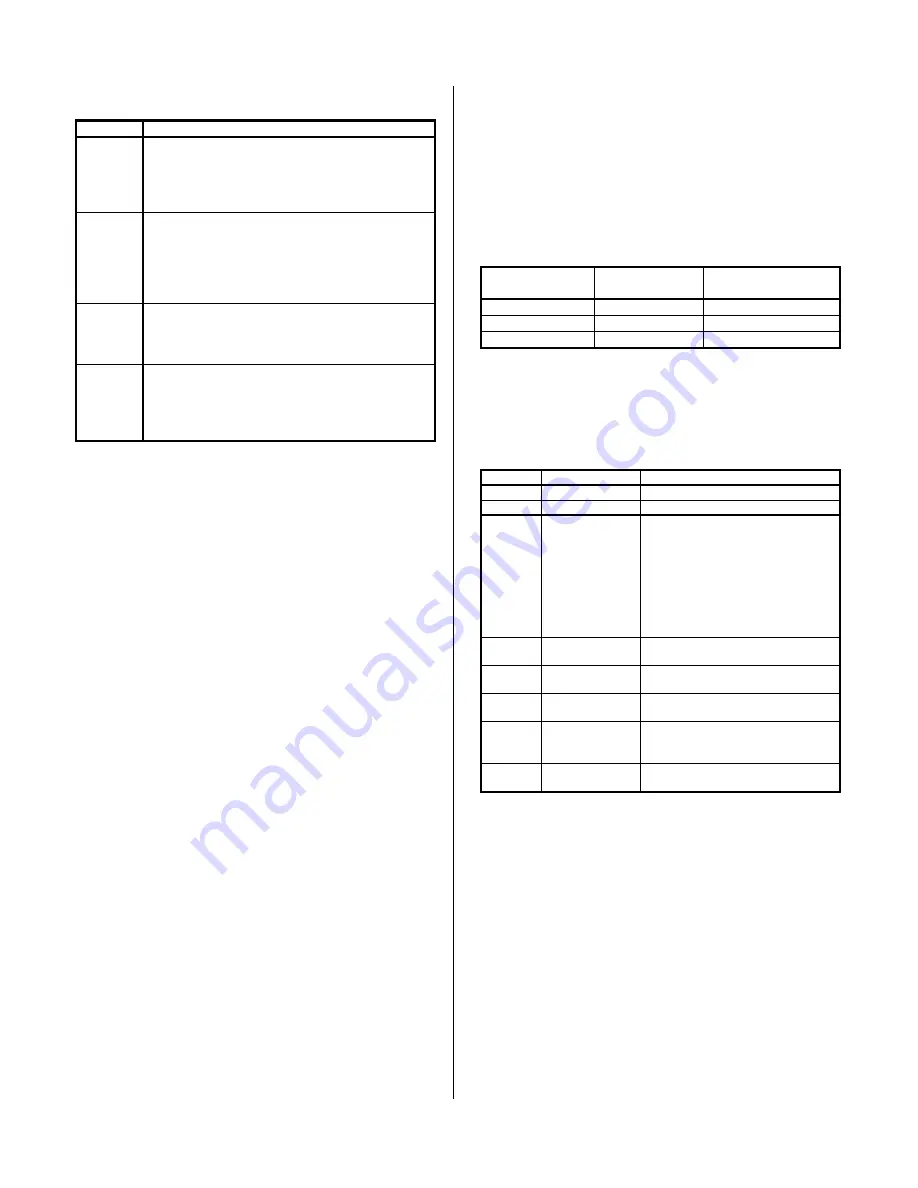

MSR - Modem Status Register continued

MSR BIT

FUNCTION

4

CTS - the complement of the CTS* input from the

modem indicating that the modem is ready to

receive data. If the channel is in the loopback

mode (MCR bit 4 = 1), then the state of RTS in the

MCR is reflected

5

DSR - the complement of the DSR* input from the

modem indicating that the modem is ready to

provide received data to the serial channel receiver

circuitry. If the channel is in the loopback mode

(see MCR bit 4 description), then the state of DTR

in the MCR is reflected

6

RI - the complement of the RI* input from the

modem. If the channel is in the loopback mode

(see MCR bit 4 description), this bit reflects the

state of OUT1 in the MCR

7

DCD - the current status of the DCD* input from the

modem (a “1” indicates DCD* is asserted)If the

channel is in the loopback mode (see MCR bit 4

description), this bit reflects the value of OUT2 in

the MCR

An Asterisk (*) is used to indicate an active-low signal

Note that reading MSR clears the delta-modem status

indications (bits 0-3), but has no effect on the other status bits.

For the MSR & LSR registers, the setting of the status bits during

a status register read operation is inhibited (the status bit will not

be set until the trailing edge of the read)However, if the same

status condition occurs during a read operation, that status bit is

cleared on the trailing edge of the read instead of being set again

In Loopback Mode, when the modem status interrupts are

enabled, the CTS*, DSR*, RI*, and DCD* inputs are ignored.

However, a modem status interrupt can still be reflected by

writing to MCR bits 3-0 (see Loopback Mode Operation section

for details)

A power-up or system reset sets MSR bits 0-3 to 0 (bits 4-7

are determined by the corresponding input signals)

SCR - Scratch Pad/Interrupt Vector Register, Ports A & B

(R/W)

This 8-bit read/write register has no effect on the operation of

either serial channel. It is provided as an aide to the programmer

to temporarily hold data. Alternately, it stores the interrupt vector

for the serial port

If interrupt generation is desired, then this port is used to

store the interrupt vector for the serial port In response to an

interrupt select cycle, the IP module will execute a read of this

register for the interrupting port (see Interrupt Generation section

for more details)

LPT - Line Printer Data Register (Read/Write)

This register reads or writes the parallel data lines. This

register is either output only, or bi-directional, depending on the

state of the extended mode bit (bit 0 of the LEM register) and the

data-direction control bit (bit 5 of the LPC register)

If the extended mode bit is 0, then the compatibility mode is

selected and reads to the LPT register return the last data that

was written to the port, while write operations immediately output

data to the parallel data lines

If the extended mode bit is 1, then read operations return

either the last data written to the port (if the direction bit of the

LPC register is set to write/0), or the data that is present in the

port (if the direction bit is set to read/1)Write operations to this

port always latch data into the output register, but only drive the

parallel data lines when the direction bit is set to write

The following table summarizes the functionality of this port

based on the logic states of the extended mode bit and data

direction bit (bit 5 of LPC):

Extended Mode

Bit (LEM Bit 0)

Data Direction

Bit (LPC Bit 5)

Parallel Port

Function

0

X

PC/AT Mode - Output

1

0

PS/2 Mode - Output

1

1

PS/2 Mode - Input

LPS - Line Printer Status Register (Read Only)

This is a read-only status register that contains interrupt and

printer status of the line printer interface pins. These pins are

defined as follows:

Line Printer Status Register

LPS Bit

FUNCTION

PROGRAMMING

0

Reserved

Read as 1

1

Reserved

Read as 1

2

Printer

Interrupt Status

Bit (PRINT*)

When low, indicates that the

printer has acknowledged the

previous transfer with an ACKN

handshake (if bit 4 of LPC is set

to 1)This bit is set to 0 on the

active-to-inactive transition of the

ACKN* signal. The default value

is “1” and this bit is set to 1 after a

read of the status port

3

Error Status Bit

(ERR*)

Active low, corresponds to ERR*

input line state

4

Select Status

Bit (SLCT)

Corresponds to SLCT input line

state

5

Paper-Empty

Status Bit (PE)

Corresponds to the PE input line

state

6

Acknowledge

Status bit

(ACKN*)

Active low, corresponds to the

ACKN* input line state

7

Busy Status Bit

(BUSY*)

Active low, corresponds to the

active high BUSY input line state

An Asterisk (*) is used to indicate an active-low signal

Note that bits 0 & 1 are always high, bit 2 defaults to high,

and the state of bits 3-7 are dependent upon the printer device

inputs. Refer to Section 40 (Theory of Operation) for a detailed

description of the Centronics port signal functions

LPC - Line-Printer Control Register (Read/Write)

This is a Line-Printer Control register (LPC) used to control

the data direction of the parallel data lines and drive the printer

control lines. Write operations set or reset these bits, while read

operations return the state of the last write operation to this

register. The functions of these bits are defined as follows: