SERIES IP503 INDUSTRIAL I/O PACK EIA/TIA-232E & CENTRONICS COMMUNICATION MODULE

___________________________________________________________________________________________

- 14 -

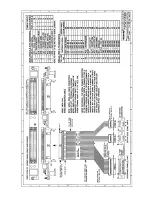

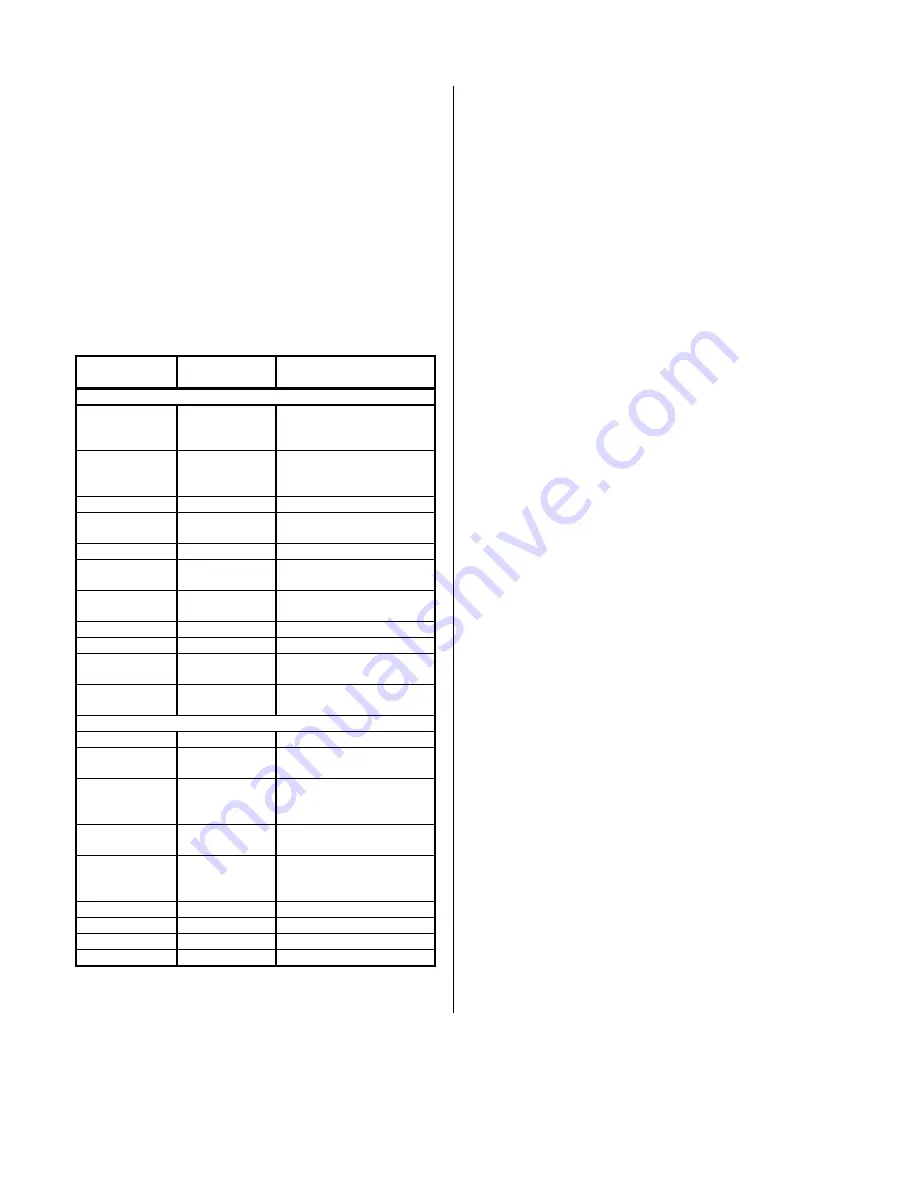

THE EFFECT OF RESET

A software or hardware reset puts the serial channels into an

idle-mode until initialization (programming)A reset initializes the

receiver and transmitter clock counters. It also clears the Line

Status Register (LSR), except for the Transmitter Shift-Register

Empty (TEMT) and Transmit Holding-Register Empty (THRE) bits

which are set to 1 (note that when interrupts are subsequently

enabled, an interrupt will occur due to THRE being set)The

Modem Control Register (MCR) is also cleared. All of the

discrete signal lines, memory elements, and miscellaneous logic

associated with these register bits are cleared, deasserted, or

turned off. However, the Line Control Register (LCR), divisor

latches, receiver buffer register, and transmitter buffer register

are not affected. The following table summarizes the effect of a

reset on the various registers and internal/external signals:

REGISTER/

SIGNAL

RESET

CONTROL

STATE/ EFFECT

REGISTERS:

IER

Reset

All Bits low (Bits 0-3

forced low, Bits 4-7

permanently low)

IIR

Reset

Bit 0 high, Bits 1,2,3,6,7

low, Bits 4 & 5

permanently low

LCR

Reset

All bits low

MCR

Reset

All bits low (bits 5-7

permanently low)

FCR

Reset

All bits low

LSR

Reset

All bits low, except bits 5

& 6 are high

MSR

Reset

Bits 0-3 low, bits 4-7 per

corresponding input signal

LPC

Reset

All Bits low

LIV

Reset

All bits low

LEM

Reset

Bit 0 low (Bits 1-7 not

used)

LIM

Reset

Bit 0 high (PS-2 Mode)

(Bits 1-7 not used)

SIGNALS (INTERNAL & EXTERNAL):

TxD

Reset

High

Interrupt

(RCVR errors)

Read LSR/

Reset

Low

Interrupt

(RCVR data

ready)

Read RBR/

Reset

Low

Interrupt

(THRE)

Read IIR/Write

THR/Reset

Low

Interrupt

(Modem Status

Changes)

Read MSR/

Reset

Low

RTS*

Reset

High

DTR*

Reset

High

OUT1*

Reset

High

OUT2*

Reset

High

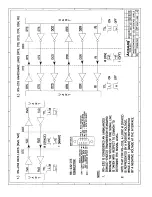

IP503 PROGRAMMING

Each serial channel of this module is programmed by the

control registers: LCR, IER, DLL, DLM, MCR, and FCR. These

control words define the character length, number of stop bits,

parity, baud rate, and modem interface. The control registers can

be written in any order, but the IER register should be written last

since it controls the interrupt enables. The contents of these

registers can be updated any time the serial channel is not

transmitting or receiving data

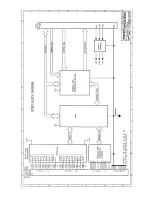

The complete status of each channel can be read by the host

CPU at any time during operation. Two registers are used to

report the status of a serial channel: the Line Status Register

(LSR) and the Modem Status Register (MSR)A third register, the

Line Printer Status Register (LPS), monitors the status of the

Centronics parallel port

Serial channel data is read from the Receiver Buffer Register

(RBR), and written to the Transmitter Holding Register

(THR)Writing data to the THR initiates the parallel-to-serial

transmitter shift register to the TxD line. Likewise, input data is

shifted from the RxD pin to the Receiver Buffer Register as it is

received. Parallel data is written to or read from the Line Printer

Data Register (LPT)

The Scratchpad/Interrupt Vector Register is used to store the

interrupt vector for the port In response to an interrupt select

cycle, the IP module will provide a read of this port register. As

such, each port may have a unique interrupt vector assigned.

Interrupts are served in a shifting-priority fashion as a function of

the last interrupting port serviced to prevent continuous interrupts

from a higher-priority interrupt channel from freezing out service

of a lower priority channel

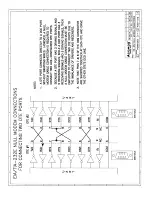

This board operates in two different modes. In one mode,

this device remains software compatible with the industry

standard 16C450 family of UART’s and provides double-buffering

of data registers. In the FIFO mode (enabled via bit 0 of the FCR

register), data registers are FIFO-buffered so that read and write

operations can be performed while the UART is performing serial-

to-parallel and parallel-to-serial conversions

Two FIFO modes of operation are possible: FIFO Interrupt

Mode and FIFO Polled Mode. In FIFO Interrupt Mode, data

transfer is initiated by reaching a pre-determined trigger-level or

generating a time-out condition. In FIFO-Polled Mode, there is no

time-out condition indicated or trigger-level reached. The

transmit and the receive FIFO’s simply hold characters and the

Line Status Register must be read to determine the channel

status

Acromag provides an Industrial I/O Pack Software Library

diskette (Model IPSW-LIB-M03, MSDOS format) to simplify

communication with the board. Example software functions are

provided for both ISAbus (PC/AT) and VMEbus applicatIons. All

functions are written in the “C” programming language and can be

linked to your applicatIon. For more details, refer to the

“READMETXT” file in the root directory on the diskette and the

“INFO503TXT” file in the appropriate “IP503” subdirectory off of

“\VMEIP” or “\PCIP”, according to your carrier