SERIES IP503 INDUSTRIAL I/O PACK EIA/TIA-232E & CENTRONICS COMMUNICATION MODULE

___________________________________________________________________________________________

- 9 -

The four lower order bits of this register are used to identify

the interrupt pending as follows:

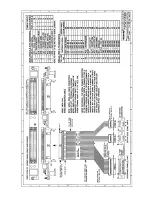

Interrupt Identification Register

BITS

3-0

INT

PRTY

INTERRUPT

TYPE

INTERRUPT

SOURCE

RESET

CONTROL

0001

--

None

None

--

0110

1st

Receiver

Line Status

OE, PE, FE,

or BI (See

LSR Bits 1-4)

LSR Read

0100

2nd

Received

Data

Available

Receiver Data

Available or

Trigger Level

Reached

RBR Read

till FIFO

below

trigger

level

1100

2nd

Character

Time-out

Indication

No characters

have been

removed from

or input to the

Rx FIFO

during last 4

character

times and

there is at

least 1

character in it

during this

time

RBR Read

0010

3rd

THRE (LSR

Bit 5)

THRE

(LSR Bit 5)

IIR Read

(if LSR bit

5 is the

interrupt

source) or

a THR

Write

0000

4th

Modem

Status

CTS*, DSR*,

RI*, or DCD*

asserted

MSR Read

From the table above, note that IIR bit 0 can be used to

indicate whether an interrupt is pending (bit 0 is low when an

interrupt is pending)IIR bits 1 & 2 are used to indicate that the

highest priority interrupt is pending. IIR bit 3 is always logic 0

when in the 16C450 modeI. IR bit 3 is set along with bit 2 when

in the FIFO mode and when a time-out interrupt is pending

Bits 4 and 5 of this register are always set to 0Bits 6 and 7

are set when bit 0 of the FIFO Control Register is set to 1A

power-up or system reset sets IIR bit 0 to 1, bits 1,2,3,6, and 7 to

0, while bits 4 & 5 are permanently low

FCR - FIFO Control Register, Ports A & B (WRITE Only)

This write-only register is used to enable and clear the FIFO

buffers, set the trigger level of the Rx FIFO, and select the type of

DMA signaling (DMA is NOT supported by this model)

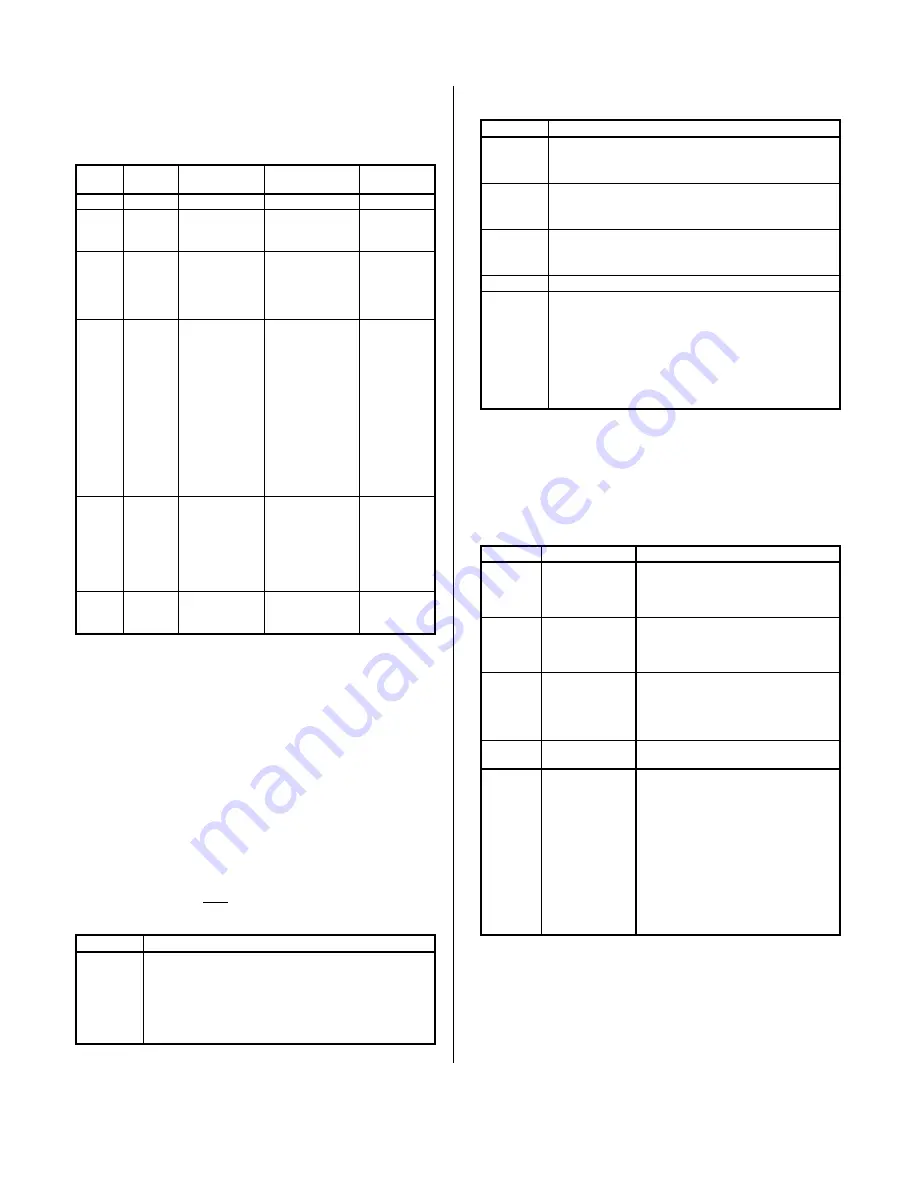

FIFO Control Register

FCR BIT

FUNCTION

0

When set to “1”, this bit enables both the Tx and Rx

FIFO’s. All bytes in both FIFO’s can be cleared by

resetting this bit to 0Data is cleared automatically

from FIFO’s when changing from FIFO mode to

alternate mode and visa-versa. Programming of

other FCR bits is enabled by setting this bit to 1

FIFO Control Register continued

FCR BIT

FUNCTION

1

When set to “1”, this bit clears all bytes in the Rx-

FIFO and resets the counter logic to 0 (this does

not clear the shift register)

2

When set to “1”, this bit clears all bytes in the Tx-

FIFO and resets the counter logic to 0 (this does

not clear the shift register)

3

When set to “1”, this bit sets DMA Signal from

Mode 0 to Mode 1, if FIFO Control Register Bit 0 =

1 (DMA Not Supported)

4,5

Not Used

6,7

Used for setting the trigger level of the Rx FIFO

interrupt as follows:

BIT 7-6Rx-FIFO TRIGGER LEVEL

0001 Bytes

0104 Bytes

1008 Bytes

1114 Bytes

A power-up or system reset sets all FCR bits to 0

LCR - Line Control Register, Ports A & B (Read/Write)

The individual bits of this register control the format of the

data character as follows:

Line Control Register

LCR Bit

FUNCTION

PROGRAMMING

1 and 0

Word Length

Select

0 0 = 5 Data Bits

0 1 = 6 Data Bits

1 0 = 7 Data Bits

1 1 = 8 Data Bits

2

Stop Bit

Select

0 = 1 Stop Bit

1 = 15 Stop Bits if 5 data bits

selected; 2 Stop Bits if 6, 7, or

8 data bits selected

3

Parity Enable

0 = Parity Disabled

1 = Parity Enabled

A parity bit is generated and

checked for between the last data

word bit and the stop bit

4

Even-Parity

Select

0 = Odd Parity

1 = Even Parity

5

Stick Parity

0 = Stick Parity Disabled

1 = Stick Parity Enabled

When parity is enabled, stick parity

causes the transmission and

reception of a parity bit to be in the

opposite state from the value

selected via bit 4This is used as a

diagnostic tool to force parity to a

known state and allow the receiver

to check the parity bit in a known

state