SERIES IP503 INDUSTRIAL I/O PACK EIA/TIA-232E & CENTRONICS COMMUNICATION MODULE

___________________________________________________________________________________________

- 8 -

Upon loading either latch, a 16-bit baud counter is

immediately loaded (this prevents long counts on initial load)The

clock may be divided by any divisor from 1 to 2

(16-1)

The output

frequency of the baud rate generator (RCLK) is 16x the data rate.

The relationship between the output of the baud generator

(RCLK), the baud rate, the divisor, and the 8MHz system clock

can be summarized in the following equations:

DIVISOR = CLOCK FREQUENCY

÷

[BAUD RATE x 16];

RCLK= 16 x BAUD RATE;

= 16 x [CLOCK

÷

(16 x DIVISOR)] = CLOCK

÷

DIVISOR

The following table shows the correct divisor to use for

generation of some standard baud rates (based on the 8MHz

clock)Note that baud rates up to 512K may be configured, but the

EIA/TIA-232E drivers of this module limit data rates to 128Kbps

maximum for performance within rated load specifications.

However, limited performance at 256Kbps and 512Kbs is

possible, but not recommended or guaranteed

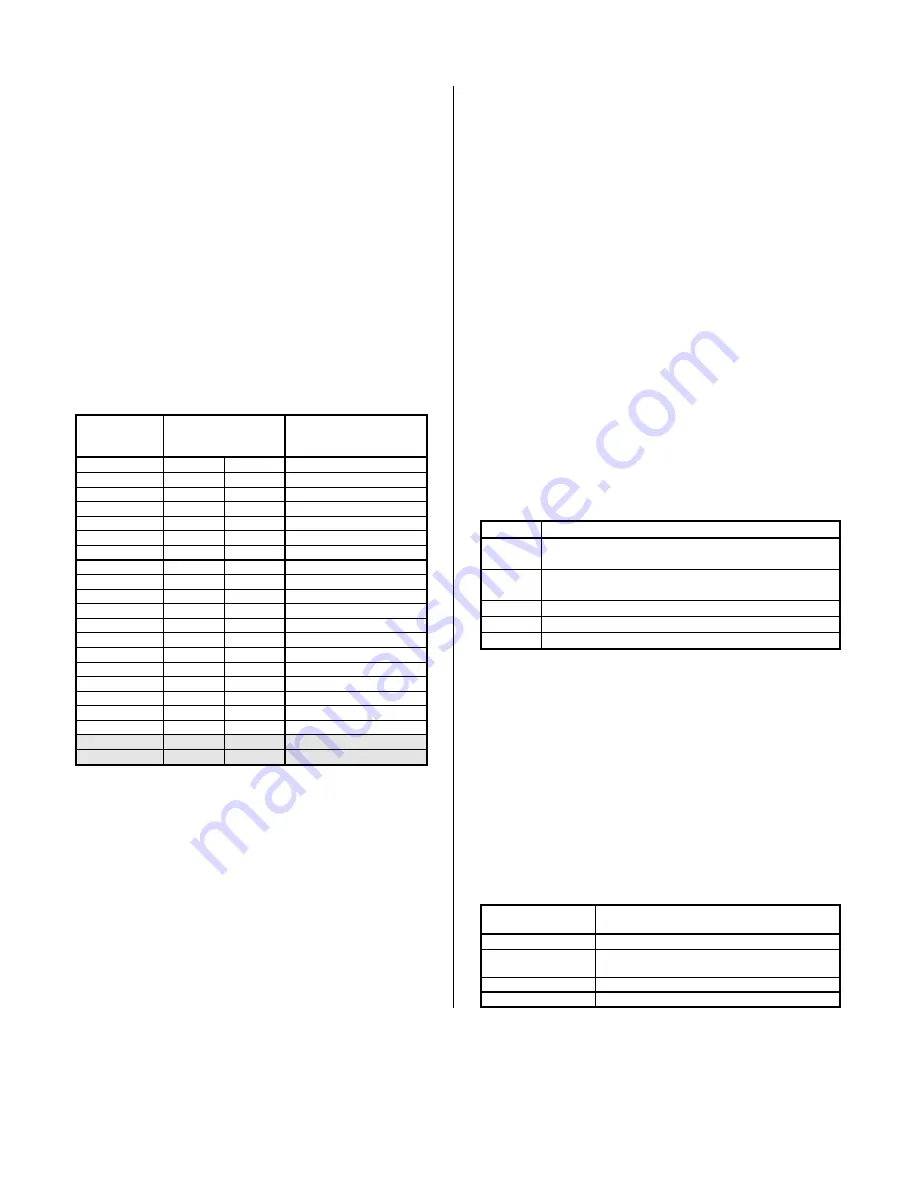

Table 32:Baud Rate Divisors and Relative Error (8MHz Clk)

BAUD RATE

DESIRED

DIVISOR (N)

USED FOR 16x

CLOCK

% ERROR DIFF BET

DESIRED & ACTUAL

50

10000

2710H

0

75

6667

1A06H

0005

110

4545

11C1H

0010

1345

3717

0E85H

0013

150

3333

0D05H

0010

300

1667

0683H

0020

600

833

0341H

0040

1200

417

01A1H

0080

1800

277

0115H

0080

2000

250

00FAH

0

2400

208

00D0H

0160

3600

139

0086H

0080

4800

104

0068H

0160

7200

69

0045H

0644

9600

52

0034H

0160

19200

26

001AH

0160

38400

13

000DH

0160

56000

9

0009H

0790

128000

4

0004H

2344

256000

2

0002H

2344

512000

1

0001H

2400

SHADED entries are not recommended due to driver limitations

With respect to this device, the baud rate may be considered

equal to the number of bits transmitted per second (bps)The bit

rate (bps), or baud rate, defines the bit time. This is the length of

time a bit will be held on before the next bit is transmitted. A

receiver and transmitter must be communicating at the same bit

rate, or data will be garbled. A receiver is alerted to an incoming

character by the start bit, which marks the beginning of the

character. It then times the incoming signal, sampling each bit as

near to the center of the bit time as possible

To better understand the asynchronous timing used by this

device, note that the receive data line (RxD) is monitored for a

high-to-low transition (start bit)When the start bit is detected, a

counter is reset and counts the 16x sampling clock to 7-1/2

(which is the center of the start bit)The receiver then counts from

0 to 15 to sample the next bit near its center, and so on, until a

stop bit is detected, signaling the end of the data stream. Use of

a sampling rate 16x the baud rate reduces the synchronization

error that builds up in estimating the center of each successive bit

following the start bit. As such, if the data on RxD is a

symmetrical square wave, the center of each successive data cell

will occur within

±

3125% of the actual center (this is 50%

÷

16,

providing an error margin of 46875%)Thus, the start bit can begin

as much as one 16x clock cycle prior to being detected

IER - Interrupt Enable Register, Ports A & B (R/W)

The Interrupt Enable Register is used to independently

enable/ disable the four possible serial channel interrupt sources

that drive the INTREQ0* line (Serial ports A & Band the parallel

port share this line)Interrupts are disabled by resetting the

corresponding IER bit low (0), and enabled by setting the IER bit

high (1)Disabling the interrupt system (IER bits 0-3 low) also

inhibits the Interrupt Identification Register (IIR) and the interrupt

request line (INTREQ0*)All other functions operate in their normal

manner, including the setting of the Line Status Register (LSR)

and the Modem Status Register (MSR)

IER BIT

INTERRUPT ACTION

0

A “1” enables the Received Data Available Interrupt

and the Time-Out Interrupts (FIFO Mode)

1

A “1” enables the Transmitter Holding Register

Empty Interrupt

2

A “1” enables the Receiver Line Status Interrupt

3

A “1” enables the Modem Status Interrupt

4-7

Not Used - Set to Logic 0

A power-up or system reset sets all IER bits to 0 (bits 0-3

forced low, bits 4-7 permanently low)

IIR - Interrupt Identification Register, Ports A & B (READ

Only)

The Interrupt Identification Register is used to indicate that a

prioritized interrupt is pending and the type of interrupt that is

pending. This register will indicate the highest-priority interrupt

pending. In order to minimize the software overhead during data

character transfers, individual serial channels prioritize their

interrupts into four levels (indicated below)Additionally, with

respect to the 2 serial ports and the parallel port, interrupts are

also served according to a shifting priority scheme that is a

function of the last interrupting port served

PRIORITY/LEVE

L

INTERRUPT

1

Receiver Line Status

2

Received Data Ready or Character Time-

out

3

Transmitter Holding Register Empty

4

Modem Status