SERIES IP503 INDUSTRIAL I/O PACK EIA/TIA-232E & CENTRONICS COMMUNICATION MODULE

___________________________________________________________________________________________

- 6 -

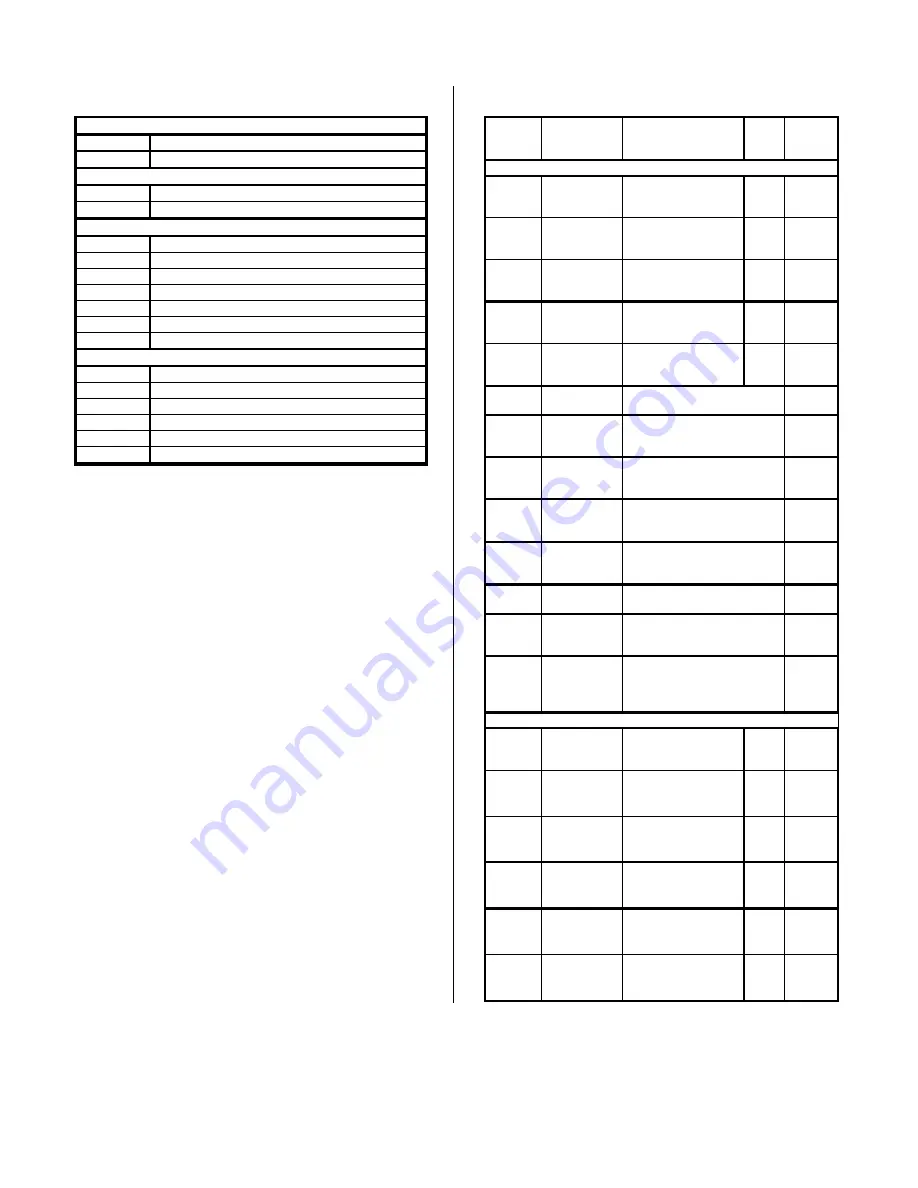

IP503 Data, Status, and Control Registers

SERIAL DATA REGISTERS (Per Serial Port):

RBR

Receive Buffer Register

THR

Transmitter Holding Register

SERIAL STATUS REGISTERS (Per Serial Port):

LSR

Line Status Register

MSR

Modem Status Register

SERIAL CONTROL REGISTERS (Per Serial Port):

LCR

Line Control Register

FCR

FIFO Control Register

MCR

Modem Control Register

DLL

Divisor Latch LSB

DLM

Divisor Latch MSB

IER

Interrupt Enable Register

SCR

Scratch Pad/Interrupt Vector Register

CENTRONICS PORT REGISTERS:

LPT

Parallel Read/Write Data Register

LPS

Parallel Read Status Register

LPC

Parallel Read/Write Control Register

LEM

Line Printer Extended Mode Select (R/W)

LIM

Line Printer Interrupt Mode Select (R/W)

LIV

Line Printer Interrupt Vector Register (R/W)

The I/O space may be as large as 64, 16-bit words (128

bytes) using address lines A1A6,but the IP503 uses only a

portion of this space. The I/O space address map for the IP503

is shown in Table 31Note the base address for the IP module I/O

space (see your carrier board instructions) must be added to the

addresses shown to properly access the I/O space. All accesses

are performed on an 8-bit word basis (D0D7)

This manual is presented using the “Big Endian” byte

ordering format. Big Endian is the convention used in the

Motorola 68000 microprocessor family and is the VMEbus

convention. In Big Endian, the lower-order byte is stored at odd-

byte addresses. Thus, byte accesses are done on odd address

locations. The Intel x86 family of microprocessors use the

opposite convention, or “Little Endian” byte ordering. Little

Endian uses even-byte addresses to store the low-order byte. As

such, use of this module on an ISAbus (PC/AT) carrier board will

require the use of the even address locations to access the 8-bit

data, while a VMEbus carrier will require the use of odd address

locations

Note that some functions share the same register address.

For these items, the address lines are used along with the divisor

latch access bit (bit 7 of the Line Control Register) and/or the

read and write signals to determine the function required.

Beyond the first two address locations for each serial port, the

state of the divisor latch access bit is irrelevant

Table 31:IP503 R/W Space Address (Hex) Memory Map

Base

Addr+

MSB

D15D08

LSB

D07 D00

LC

R

Bit7

Base

Addr+

Serial Port A Registers:

00

Not Driven

1

READ - RBR

Port A Receiver

Buffer Register

0

01

00

Not Driven

1

WRITE - THR

Port A Transmitter

Holding Register

0

01

00

Not Driven

1

R/W - DLL

Port A Divisor

Latch LSB

1

01

02

Not Driven

1

R/W - IER

Port A Interrupt

Enable Register

0

03

02

Not Driven

1

R/W - DLM

Port A Divisor

Latch MSB

1

03

Base

Addr+

MSB

D15D08

LSB

D07 D00

Base

Addr+

04

Not Driven

1

READ - IIR

Port A Interrupt

Identification Register

05

04

Not Driven

1

WRITE - FCR

Port A FIFO Control

Register

05

06

Not Driven

1

R/W - LCR

Port A Line Control

Register

07

08

Not Driven

1

R/W - MCR

Port A Modem Control

Register

09

0A

Not Driven

1

R/W - LSR

Port A Line Status Register

0B

0C

Not Driven

1

R/W - MSR

Port A Modem Status

Register

0D

0E

Not Driven

1

R/W - SCR

Port A Scratch

Pad/Interrupt Vector

Register

0F

Serial Port B Registers:

Base

Addr+

MSB

D15D08

LSB

D07 D00

LC

R

Bit7

Base

Addr+

10

Not Driven

1

READ - RBR

Port B Receiver

Buffer Register

0

11

10

Not Driven

1

WRITE - THR

Port B Transmitter

Holding Register

0

11

10

Not Driven

1

R/W - DLL

Port B Divisor

Latch LSB

1

11

12

Not Driven

1

R/W - IER

Port B Interrupt

Enable Register

0

13

12

Not Driven

1

R/W - DLM

Port B Divisor

Latch MSB

1

13