VersaGateway User’s Manual

Document #: 2015006.1.pdf

PAGE 30 of 44

Divelbiss Corporation • 9778 Mt. Gilead Road • Fredericktown, Ohio 43019 • 1-800-245-2327 • www.divelbiss.com

Device Features

EEPROM Memory (ON-CHIP)

The VersaGateway Devices support two types of on-board non-volatile memory: EEPROM and FRAM. The EEPROM memory is on-

chip (on-board the PLC on a Chip) while the FRAM is an independent device.

EEPROM memory is often useful for storing setpoint values into memory that will hold its value in the event of a loss of power.

EEPROM memory is a relatively slow writing device (in terms of milliseconds) and has limitations. This EEPROM memory is located

on the PLC on a Chip itself (PLCHIP-P13-51220).

EEPROM memory should not be used in applications where the values are updated (causing the stored value to update)

often; such as a process variable. While EEPROM memory has a long life, repeated writing (thousands of times) can cause

a memory location to fail. EEPROM memory is more oriented to be used for storage of menu changeable setpoints that

may change, but infrequently.

CONFIGURING THE ON CHIP EEPROM IN EZ LADDER TOOLKIT

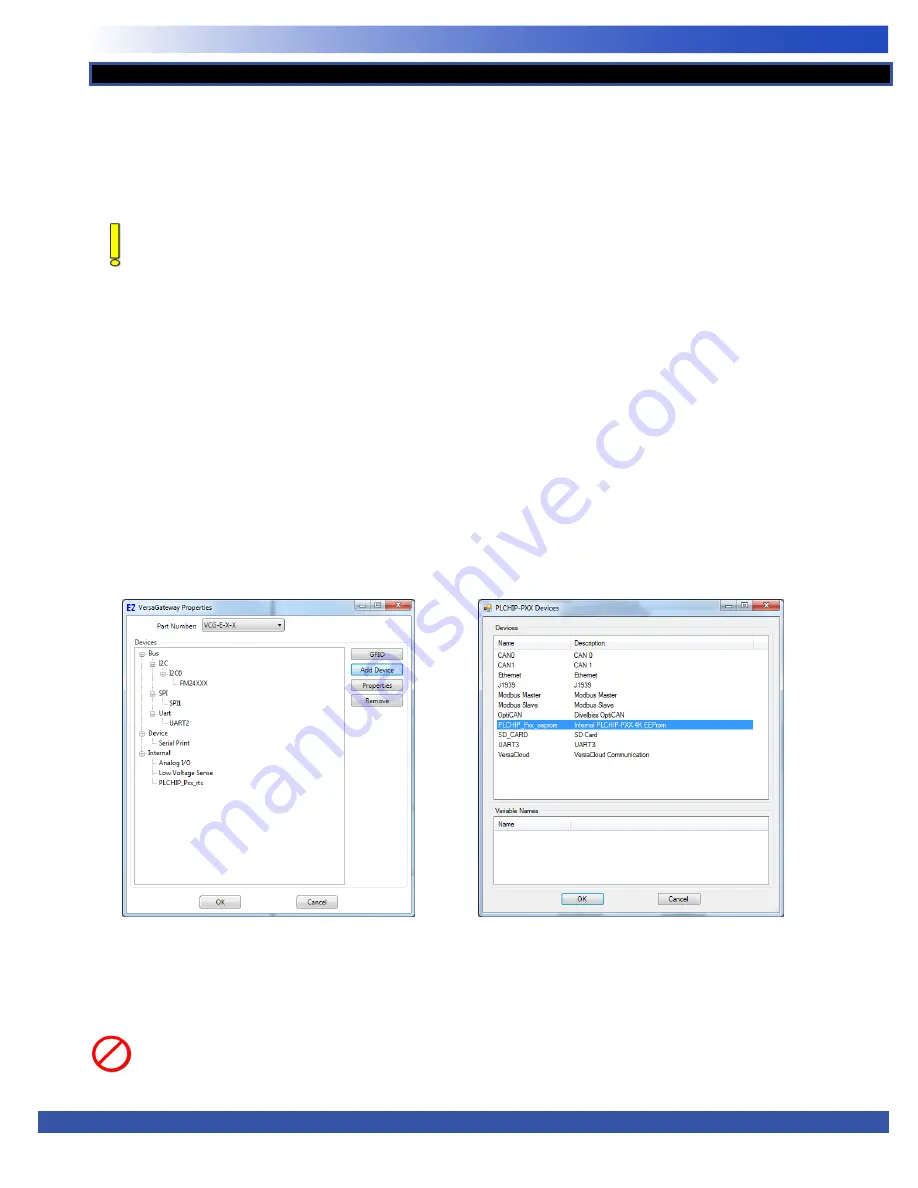

Before the PLC on a Chip on-board EEPROM may be used in the ladder diagram, it must be added to the program’s target settings

using the EZ LADDER Toolkit’s Project Settings Menu.

1. In EZ LADDER, from the File Menu at the top, click

PROJECT

then

SETTINGS

. This will open the Project Settings Window.

Select

VersaGateway

as the target from the choices.

2. Click the

PROPERTIES

button to the right side of the window. The

VersaGateway’s Properties

Window will open. Make sure

the proper model is selected in the drop-down menu. If the EEPROM feature was already installed, it would be displayed in

the Devices Pane under the

Internal

heading (as PLCHIP_Pxx_eeprom). Refer to Figure 2-27.

3. Click the

ADD DEVICE

button. The

PLCHIP-PXX Devices

window will open. Locate the

PLCHIP_Pxx_eeprom

in the Devices pane

of this window.

4. Click the

PLCHIP_Pxx_eeprom

device (highlight). Refer to Figure 2-28.

Figure 2-27 - VersaGateway Properties

Figure 2-28 - PLCHIP-PXX Devices - EEPROM

5. Click

OK

. The

PLCHIP_Pxx_eeprom Properties

dialog will open. Leave the default settings (Num Retentive Bytes set to 0). See

Figure 2-29. Click

OK

.

The VersaGateway’s On-Chip EEPROM should not be used for Retentive Memory. All Retentive features should be

configured to use FRAM. Using on-chip EEPROM for retentive features will result in retentive data being lost.