SERIES IP330 INDUSTRIAL I/O PACK 16-BIT HIGH DENSITY ANALOG INPUT MODULE

___________________________________________________________________________________________

- 6 -

Analog Inputs: Noise and Grounding Considerations

Differential inputs require two leads (+ and -) per channel, and

provide rejection of common mode voltages. This allows the

desired signal to be accurately measured. However, the signal

being measured cannot be floating--it must be referenced to

analog common on the IP module and be within the normal input

voltage range.

Differential inputs are the best choice when the input channels

are sourced from different locations having slightly different ground

references and when minimizing noise and maximizing accuracy

are key concerns. See Drawing 4501-591 for analog input

connections for differential and single-ended inputs. Shielded

cable of the shortest length possible is also strongly

recommended.

Single-ended inputs only require a single lead (+) per channel,

with a shared "sense" (reference) lead for all channels, and can be

used when a large number of input channels come from the same

location (e.g. printed circuit board). The channel density doubles

when using single-ended inputs, and this a powerful incentive for

their use. However, caution must be exercised since the single

"sense" lead references all channels to the same common which

will induce noise and offset to the degree they are different.

The IP330 is non-isolated, since there is electrical continuity

between the logic and field I/O grounds. As such, the field I/O

connections are not isolated from the carrier board and backplane.

Care should be taken in designing installations without isolation to

avoid noise pickup and ground loops caused by multiple ground

connections. This is particularly important for analog inputs when

a high level of accuracy/resolution is needed. Contact your

Acromag representative for information on our many isolated

signal conditioning products that could be used to interface to the

IP330 input module.

External Trigger Input/Output

The external trigger signal on pin 49 of the P2 connector can

be programmed to input a TTL compatible external trigger signal,

or output IP330 hardware generated triggers to allow

synchronization of multiple IP330s.

As an input, the external trigger must be a 5 Volt logic, TTL-

compatible, debounced signal referenced to analog common. The

external trigger signal is an active low edge sensitive signal. That

is, the external trigger signal will trigger the IP330 hardware on the

falling edge. Once the external trigger signal has been driven low,

it should remain low for a minimum of 500n seconds.

As an output an active-low TTL signal can be driven to

additional IP330s, thus providing a means to synchronize the

conversions of multiple IP330s. The additional IP330s must

program their external trigger for signal input and convert on

external trigger only mode. See section 3.0 for programming

details to make use of this signal.

IP Logic Interface Connector (P1)

P1 of the IP module provides the logic interface to the mating

connector on the carrier board. This connector is a 50-pin female

receptacle header (AMP 173279-3 or equivalent) which mates to

the male connector of the carrier board (AMP 173280-3 or

equivalent). This provides excellent connection integrity and

utilizes gold-plating in the mating area. Threaded metric M2

screws and spacers are supplied with the IP module to provide

additional stability for harsh environments (see Drawing 4501-434

for assembly details). Field and logic side connectors are keyed to

avoid incorrect assembly. The pin assignments of P1 are

standard for all IP modules according to the Industrial I/O Pack

Specification (see Table 2.4).

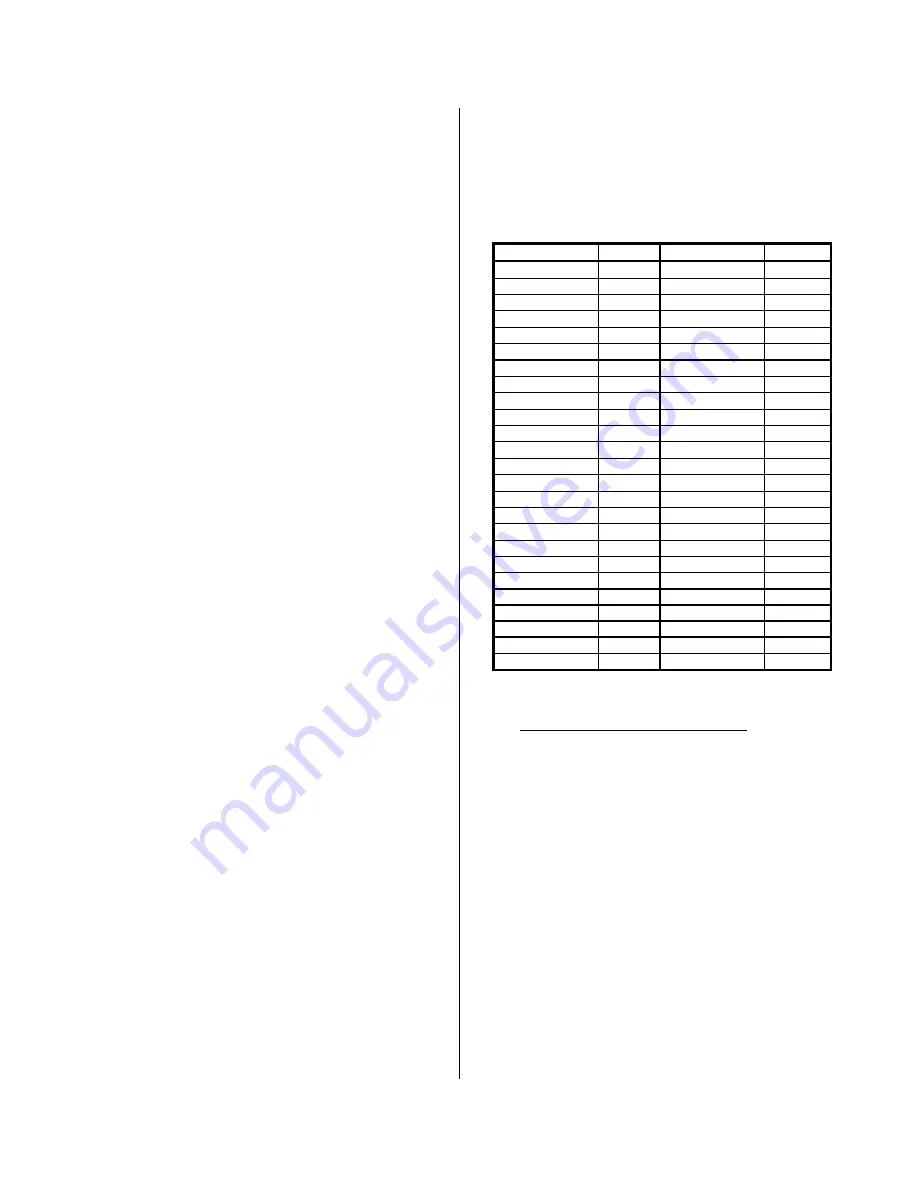

Table 2.4: Standard Logic Interface Connections (P1)

Pin

Description Number Pin

Description Number

GND 1 GND 26

CLK 2 +5V 27

Reset* 3 R/W* 28

D00 4

IDSEL*

29

D01 5

DMAReq0*

30

D02 6

MEMSEL*

31

D03 7

DMAReq1*

32

D04 8

IntSel*

33

D05 9

DMAck0*

34

D06 10

IOSEL*

35

D07 11

RESERVED

36

D08 12 A1 37

D09 13

DMAEnd*

38

D10 14 A2 39

D11 15

ERROR*

40

D12 16 A3 41

D13 17

INTReq0*

42

D14 18 A4 43

D15 19

INTReq1*

44

BS0* 20 A5 45

BS1*

21

STROBE*

46

-12V 22 A6 47

+12V 23 ACK* 48

+5V 24

RESERVED

49

GND 25 GND 50

An Asterisk (*) is used to indicate an active-low signal.

BOLD ITALIC

Logic Lines are NOT USED by this IP Model.

3.0 PROGRAMMING INFORMATION

IP IDENTIFICATION PROM - (Read Only, 32 Odd-Byte

Addresses)

Each IP module contains an identification (ID) information that

resides in the ID space per the IP module specification. This area

of memory contains 32 bytes of information at most. Both fixed

and variable information may be present within the ID space.

Fixed information includes the "IPAC" identifier, model number,

and manufacturer's identification codes. Variable information

includes unique information required for the module. The IP330 ID

information does not contain any variable (e.g. unique calibration)

information. ID space bytes are addressed using only the odd

addresses in a 64 byte block (on the “Big Endian” VMEbus). Even

addresses are used on the “Little Endian” PC ISA bus. The IP330

ID space contents are shown in Table 3.1. Note that the base-

address for the IP module ID space (see your carrier board

instructions) must be added to the addresses shown to properly

access the ID space. Execution of an ID space read requires 1

wait state.