Data Sheet

136

Rev. 1.00

2017-07-31

TLE9262BQXV33

Serial Peripheral Interface

Notes

1. See also

Chapter 15.2.4

for more information on disabling the watchdog in SBC Stop Mode.

2. See

Chapter 15.2.5

for more information on the effect of the bit WD_EN_WK_BUS.

3. See

Chapter 15.2.3

for calculation of checksum.

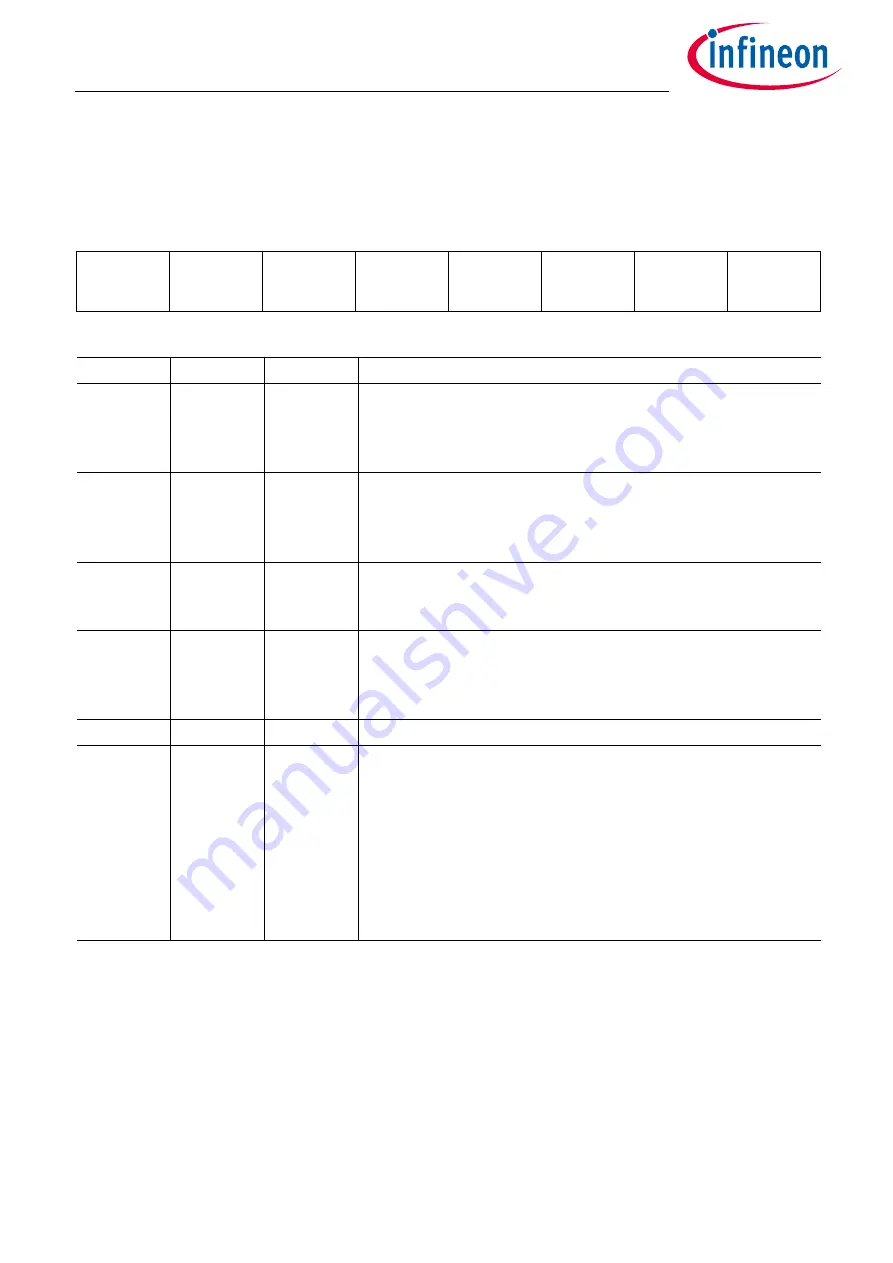

WD_CTRL

Watchdog Control (Address 000 0011

B

)

POR / Soft Reset Value: 0001 0100

B

;

Restart Value: x0xx 0100

B

7

6

5

4

3

2

1

0

CHECKSUM

WD_STM_

EN_0

WD_WIN

WD_EN_

WK_BUS

Reserved

WD_TIMER_2 WD_TIMER_1 WD_TIMER_0

r

rw

rwh

rw

rw

r

rwh

rwh

rwh

Field

Bits

Type

Description

CHECKSUM

7

rw

Watchdog Setting Check Sum Bit

The sum of bits 7:0 needs to have even parity (see

Chapter 15.2.3

)

0B , Counts as 0 for checksum calculation

1B , Counts as 1 for checksum calculation

WD_STM_

EN_0

6

rwh

Watchdog Deactivation during Stop Mode, bit 0

(

Chapter 15.2.4

)

0B , Watchdog is active in Stop Mode

1B , Watchdog is deactivated in Stop Mode

WD_WIN

5

rw

Watchdog Type Selection

0B , Watchdog works as a Time-Out watchdog

1B , Watchdog works as a Window watchdog

WD_EN_

WK_BUS

4

rw

Watchdog Enable after Bus (CAN/LIN) Wake in SBC Stop Mode

0B , Watchdog will not start after a CAN/LINx wake

1B , Watchdog starts with a long open window after CAN/LINx

Wake

Reserved

3

r

Reserved, always reads as 0

WD_TIMER

2:0

rwh

Watchdog Timer Period

000B , 10ms

001B , 20ms

010B , 50ms

011B , 100ms

100B , 200ms

101B , 500ms

110B , 1000ms

111B , reserved