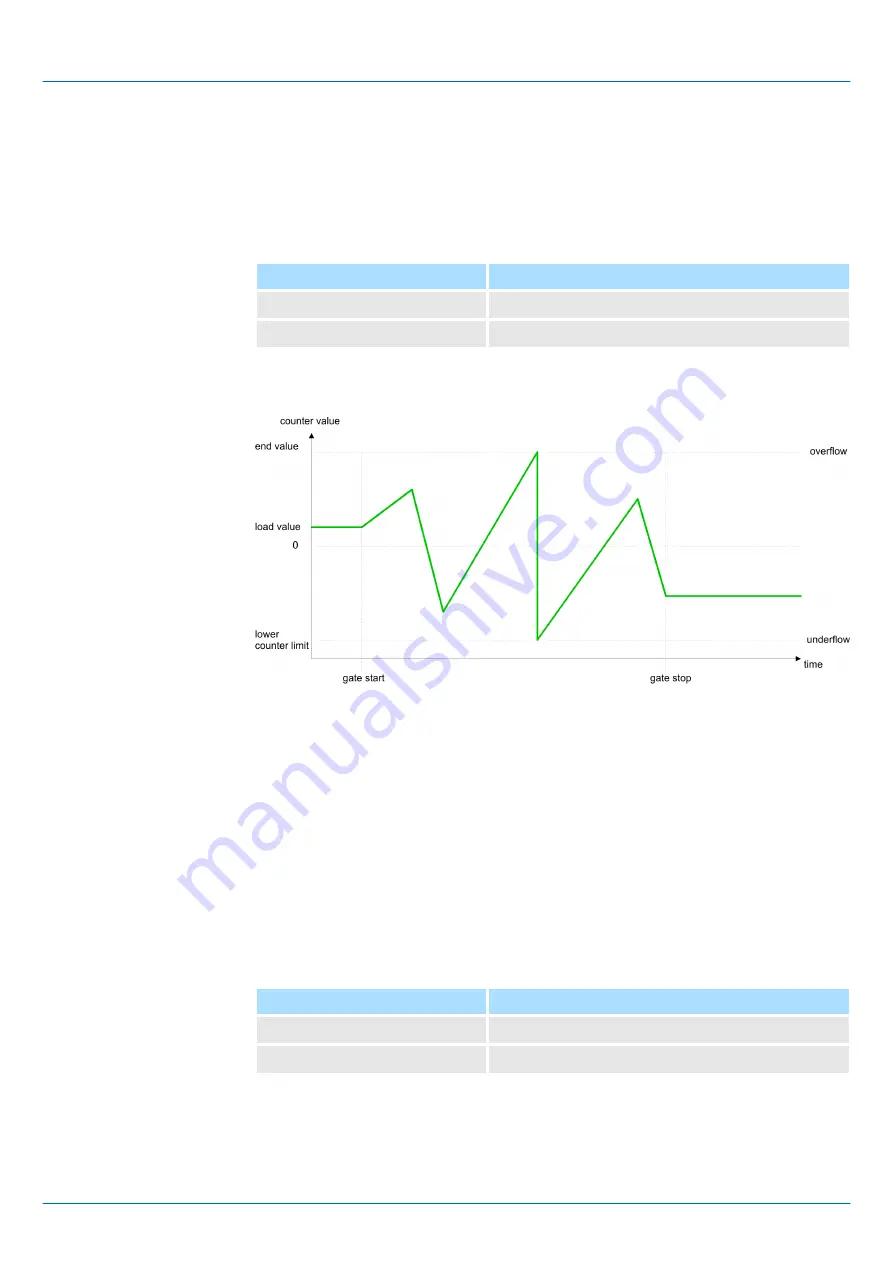

In this operating mode, the counter counts from the load value. When the counter counts

forward and reaches the upper count limit and another counting pulse in positive direction

arrives, it jumps to the lower count limit and counts from there on. When the counter

counts backwards and reaches the lower count limit and another counting pulse in nega-

tive direction arrives, it jumps to the upper count limit and counts from there on. The

count limits are set to the maximum count range.

Limits

Valid value range

Lower count limit

-2 147 483 648 (-2

31

)

Upper count limit

+2 147 483 647 (2

31

-1)

With overflow or underflow the status bits STS_OFLW respectively STS_UFLW are set.

These bits remain set until these are reset with RES_STS. If enabled additionally a

process interrupt is triggered.

No main counting direction

n

The counter counts once starting with the

load value

.

n

You may count forward or backwards.

n

The count limits are set to the maximum count range.

n

At over- or underflow at the count limits, the counter jumps to the according other

count limit and the internal gate is automatically closed and the status bits

STS_OFLW respectively STS_UFLW are set. If enabled additionally a process inter-

rupt is triggered.

n

To restart the count process, you have to re-open the internal gate.

n

At interrupting gate control, the count process continuous with the last recent

counter

value

.

n

At aborting gate control, the counter starts with the

load value

.

Limits

Valid value range

Lower count limit

-2 147 483 648 (-2

31

)

Upper count limit

+2 147 483 647 (2

31

-1)

Interrupting gate control:

Count continuously

Count Once

VIPA System 300S

+

Deployment I/O periphery

Counter > Counter - Functions

HB140 | CPU-SC | 313-5BF23 | en | 19-01

117