Rev. 1.10

108

November 26, 2019

Rev. 1.10

109

November 26, 2019

HT68FB240

USB Low Speed Flash MCU

USB Interface Operation

The device has

3

Endpoints (EP0~EP

2

). EP0 supports Control transfer for Setup, IN and OUT token

respectively. EP1

and

EP

2

support Interrupt transfer. These registers, including USB_STAT, UINT,

USC, UCC, AWR, STL, SIES, MISC, UFEN, URDCT and FIFO0~FIFO2 are used for the USB

function.

EP0, EP1 and EP2

each h

ave 8

-byte FIFO size

respectively. EP0 supports DMA interface for

Co

nfigure USB descriptor. Please reference the DMA for detail description. EP0~EP2 are equiped

with independent registers and not shared with the general data memory RAM. The Serial Interface

Engine (SIE) of the device is compatible with USB 2.0 Low speed protocol.

The

URD

in the USC register is the USB reset signal control function definition bit.

USB Interface Registers

The USB interface has a series of registers associated with its operation.

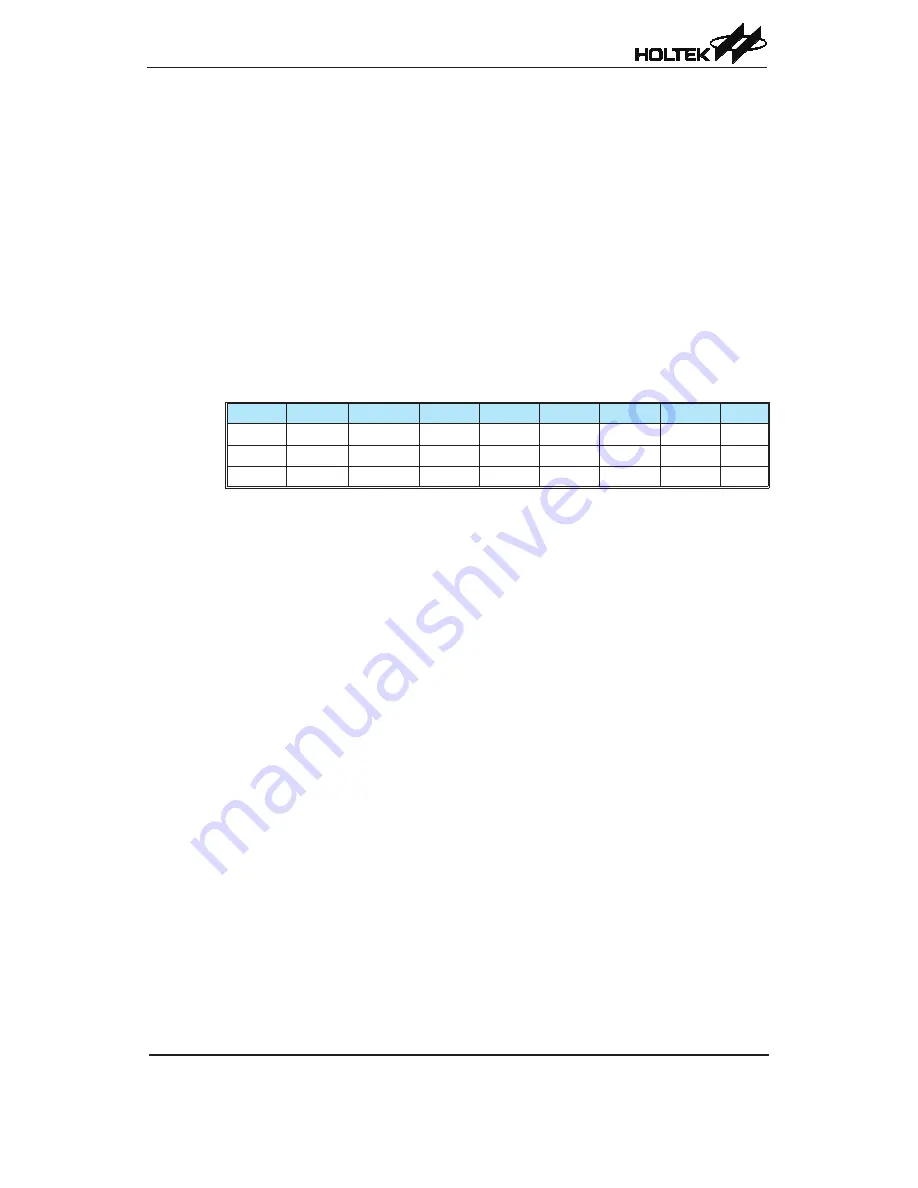

USB_STAT Register

Bit

7

6

5

4

3

2

1

0

Name

PS2_CKO PS2_DAO PS2_CKI PS2_DAI

SE1

SE0

PU

ESD

R/W

W

W

R

R

R/W

R/W

R/W

R/W

POR

1

1

x

x

0

0

0

—

"x" unknown

"-" Hardware did not give ESD bit initial value in power on reset

Bit 7

PS2_CKO:

Output for driving UDP/GPIO1 pin, when work under 3D PS2 mouse

function. Default value is "1".

Bit 6

PS2_DAO:

Output for driving UDN/GPIO

0

pin, when work under 3D PS2 mouse

function. Default value is "1".

Bit 5

PS2_CKI:

UDP/GPIO

1

input.

Bit 4

PS2_DAI:

UDN/GPIO

0

input.

Bit 3

SE1:

This bit is used to indicate the SIE has detected a SE1 noise in the USB bus. This

bit is set by SIE and clear

ed

by F/W.

Bit 2

SE0:

This bit is used to indicate the SIE has detected a SE0 noise in the USB bus. This

bit is set by SIE and clear

ed

by F/W.

Bit 1

PU:

Bit1=1, UDP and UDN have a 600kΩ pull-high

.

Bit1=0, no pull-high (default on

MCU reset)

Bit 0

ESD:

This bit will set to "1" when there is ESD issue.

This bit is set by SIE and cleared by F/W.

Hardware did not give ESD bit initial value

in power on reset.