Rev. 1.10

92

November 26, 2019

Rev. 1.10

93

November 26, 2019

HT68FB240

USB Low Speed Flash MCU

Peripheral Clock Output

The Peripheral Clock Output allows the device to supply external hardware with a clock signal

synchronised to the microcontroller clock.

Peripheral Clock Operation

As the peripheral clock output pin, PCK, is shared with I/O line, the required pin function is chosen

via PCKEN in the SIMC0 register. The Peripheral Clock function is controlled using the SIMC0

register. The clock source for the Peripheral Clock Output can originate from either the TM0 CCRP

match frequency/2 or a divided ratio of the internal f

SYS

clock. The PCKEN bit in the SIMC0 register

is the overall on/off control, setting PCKEN bit to "1" enables the Peripheral Clock, setting PCKEN

bit to "0" disables it. The required division ratio of the system clock is selected using the PCKP1

and PCKP0 bits in the same register. If the device enters the SLEEP Mode, this will disable the

Peripheral Clock output.

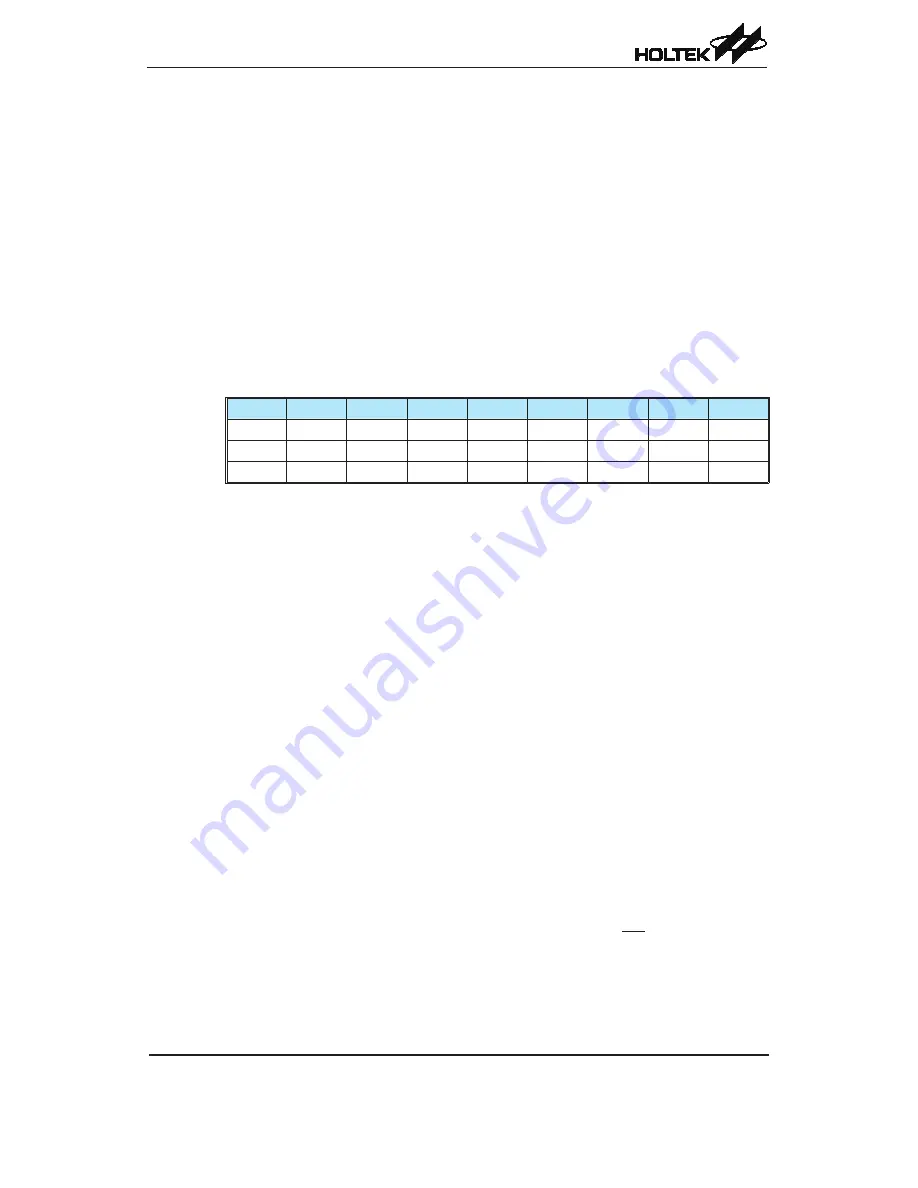

SIMC0 Register

Bit

7

6

5

4

3

2

1

0

Name

SIM2

SIM1

SIM0

PCKEN

PCKP1

PCKP0

SIMEN

—

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

—

POR

1

1

1

0

0

0

0

—

Bit 7~5

SIM2~SIM0:

SIM Operating Mode Control

000: SPI master mode; SPI clock is f

SYS

/4

001: SPI master mode; SPI clock is f

SYS

/16

010: SPI master mode; SPI clock is f

SYS

/64

011: SPI master mode; SPI clock is

f

LIRC

100: SPI master mode; SPI clock is TM0 CCRP match frequency/2

101: SPI slave mode

110: I

2

C slave mode

111: I/O mode

These bits setup the overall operating mode of the SIM function. As well as selecting

if the I

2

C or SPI function, they are used to control the SPI Master/Slave selection and

the SPI Master clock frequency. The SPI clock is a function of the system clock but

can also be chosen to be sourced from the TM0. If the SPI Slave Mode is selected then

the clock will be supplied by an external Master device.

Bit 4

PCKEN:

PCK Output Pin Control

0: Disable

1: Enable

Bit 3~2

PCKP1, PCKP0:

Select PCK output pin frequency

00: f

SYS

01: f

SYS

/4

10: f

SYS

/8

11: TM0 CCRP match frequency/2

Bit 1

SIMEN:

SIM Control

0: Disable

1: Enable

The bit is the overall on/off control for the SIM interface. When the SIMEN bit is cleared

to zero to disable the SIM interface, the SDI, SDO, SCK and

SCS

, or SDA and SCL lines

will be in a floating condition and the SIM operating current will be reduced to a minimum

value. When the bit is high the SIM interface is enabled. Note that when the SIMEN bit

changes from low to high the contents of the SPI control registers will be in an unknown

condition and should therefore be first initialised by the application program.

Bit 0

Unimplemented, read as "0"