Rev. 1.10

66

November 26, 2019

Rev. 1.10

67

November 26, 2019

HT68FB240

USB Low Speed Flash MCU

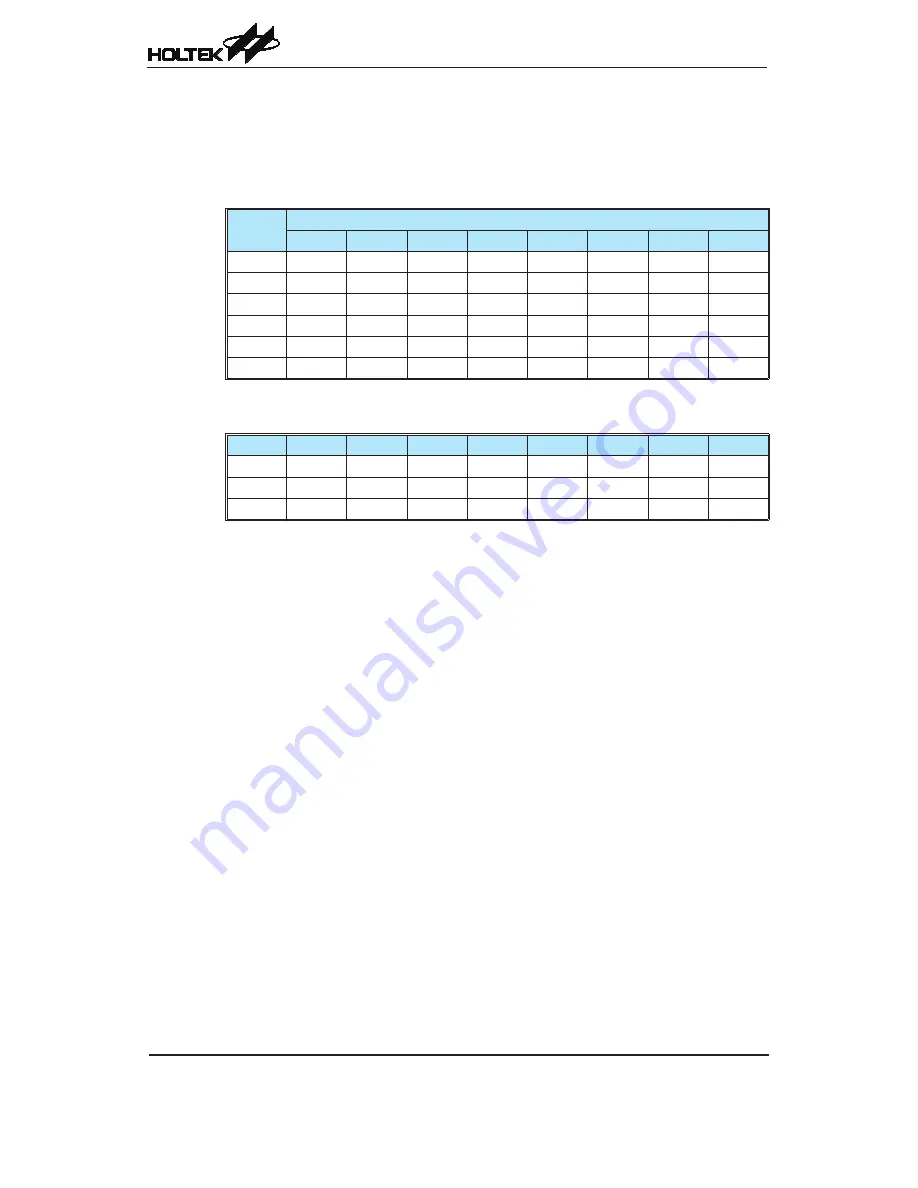

Compact Type TM Register Description

Overall operation of the Compact TM is controlled using

six registers. A read only register pair

exists to store the

internal counter 10-bit value, while a read/write register

pair exists to store the

internal 10-bit CCRA value. The

remaining two registers are control registers which

setup the

different operating and control modes as well

as the three CCRP bits.

Register

Name

Bit

7

6

5

4

3

2

1

0

TMnC0

TnPAU

TnCK2

TnCK1

TnCK0

TnON

TnRP2

TnRP1

TnRP0

TMnC1

TnM1

TnM0

TnIO1

TnIO0

TnOC

TnPOL

TnDPX

TnCCLR

TMnDL

D7

D6

D5

D4

D3

D2

D1

D0

TMnDH

—

—

—

—

—

—

D9

D8

TMnAL

D7

D6

D5

D4

D3

D2

D1

D0

TMnAH

—

—

—

—

—

—

D9

D8

Compact TM Register List (n=0, 1)

TMnC0 Register (n=0, 1)

Bit

7

6

5

4

3

2

1

0

Name

TnPAU

TnCK2

TnCK1

TnCK0

TnON

TnRP2

TnRP1

TnRP0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

POR

0

0

0

0

0

0

0

0

Bit 7

TnPAU:

TMn Counter Pause Control

0: Run

1: Pause

The counter can be paused by setting this bit high. Clearing the bit to zero restores

normal counter operation. When in a Pause condition the TM will remain powered up

and continue to consume power. The counter will retain its residual value when this bit

changes from low to high and resume counting from this value when the bit changes

to a low value again.

Bit 6~4

TnCK2~TnCK0:

Select TMn Counter clock

000: f

SYS

/4

001: f

SYS

010: f

H

/16

011: f

H

/64

100: f

LIRC

101: Undefined

110: TCKn rising edge clock

111: TCKn falling edge clock

These three bits are used to select the clock source for the TM. The external pin clock

source can be chosen to be active on the rising or falling edge. The clock source f

SYS

is

the system clock, while f

H

and f

LIRC

are other internal clocks, the details of which can

be found in the oscillator section.

Bit 3

TnON:

TMn Counter On/Off Control

0: Off

1: On

This bit controls the overall on/off function of the TM. Setting the bit high enables the

counter to run, clearing the bit disables the TM. Clearing this bit to zero will stop the

counter from counting and turn off the TM which will reduce its power consumption.

When the bit changes state from low to high the internal counter value will be reset

to zero, however when the bit changes from high to low, the internal counter will

retain its residual value. If the TM is in the Compare Match Output Mode then the TM